# **STATIC RAMs**

### **DATABOOK**

1<sup>st</sup> EDITION NOVEMBER 1989

INMOS is a member of the SGS-THOMSON Microelectronics group

# USE IN LIFE SUPPORT DEVICES FOR SYSTEMS MUST BE EXPRESSLY AUTHORIZED SGS-THOMSON PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF SGS-THOMSON Microelectronics. As used herein: Life support devices or systems are those which (a) are intended for surgical implant into the body, or (b) support 2. A critical component is any component of a life support device or system whose failure to perform can reasonaor sustain life, and whose failure to perform, when probly be expected to cause the failure of the life support perly used in accordance with instructions for use providevice or system, or to affect its safety or effectiveness. ded with the product, can be reasonably expected to result in significant injury to the user.

## **TABLE OF CONTENTS**

| INTRODUCTION                                  | Page 4    |

|-----------------------------------------------|-----------|

| QUALITY AND RELIABILITY                       | 7         |

| MILITARY QUALIFICATIONS                       | 12        |

| ALPHANUMERICAL INDEX                          | 13        |

| PRODUCT GUIDE SELECTION GUIDE CROSS REFERENCE | 17<br>23  |

| DATASHEETS COMMERCIAL SRAMS MILITARY SRAMS    | 31<br>501 |

### INTRODUCTION

The SGS-THOMSON Microelectronics Group SRAM Databook is a comprehensive collection of information on advanced, high density, high speed SRAM products for specific applications. SGS-THOMSON Microelectronics is a major supplier of a wide range of semiconductor devices, and commands leading market positions in Intelligent Power, Power Transistors, and EPROM Memories. The recent acquisition of INMOS has strengthened SGS-THOMSON's portfolio. INMOS, based in the UK, manufactures very fast SRAMs, microprocessors called transputers, color graphics products, and digital signal processing devices.

### STATIC RAMs

The SGS-THOMSON Group offer static RAM products which cover Standard SRAMs, Biport<sup>™</sup> devices, Zeropower<sup>™</sup> Timekeeper<sup>™</sup> RAMs, and Cache Tag RAMs.

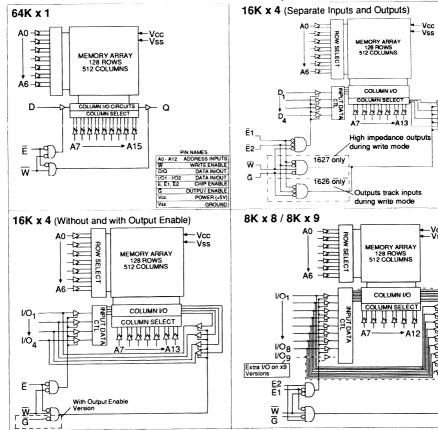

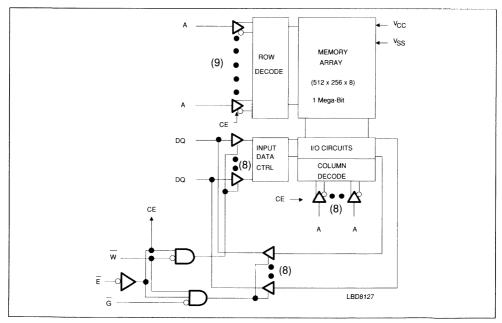

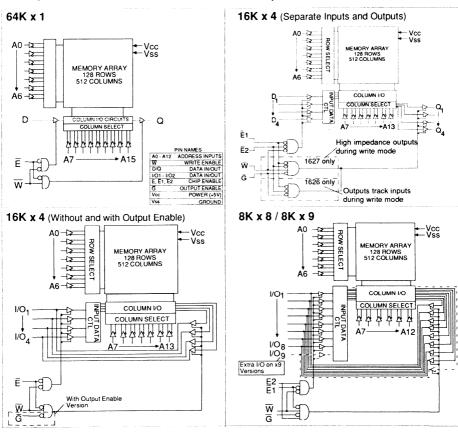

- \* Standard SRAM memories with a device density range of 4K bits to 1024k bits and performance from 15ns to 200ns. Organizational flexibility ( $4K \times 1$ ,  $1K \times 4$ ,  $16K \times 1$ ,  $4K \times 4$ ,  $64K \times 1$ ,  $16K \times 4$ ,  $8K \times 8$ ,  $8K \times 9$ ,  $256K \times 1$ ,  $64K \times 4$ ,  $32k \times 8$ ,  $128k \times 8$ ) covers a vast range of applications, including large mainframes, high speed controllers, communications, graphics display and workstations.

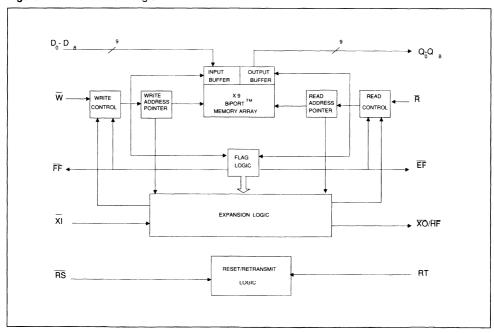

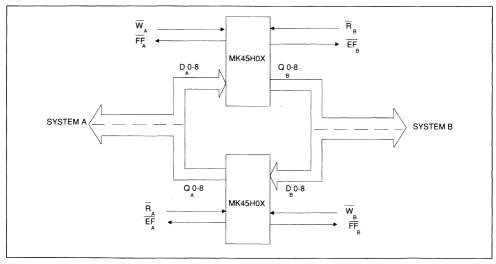

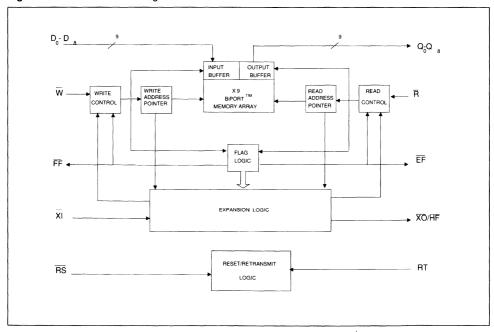

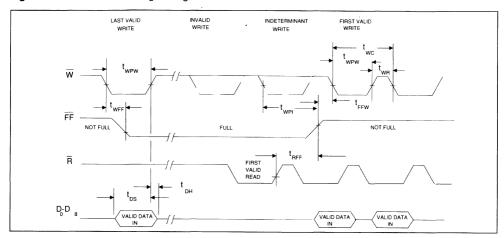

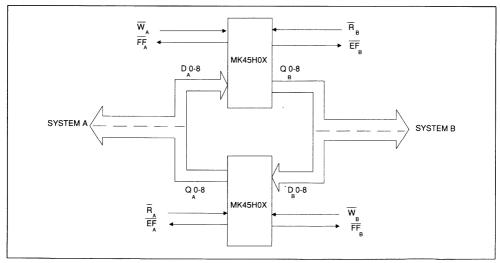

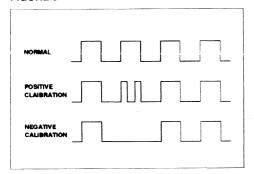

- \* BIPORT™ devices consist of a family of FIFO (First-In First-Out) buffers. These FIFOs provide an interface between digital information paths with widely varying speeds. Each information source can thus operate at its own intrinsic speed, while results are processed or distributed at speed from 25ns to 200ns. The Biport™FIFO family also includes single chip bidirectional FIFOs, and clocked FIFOs running at up 40 MHz

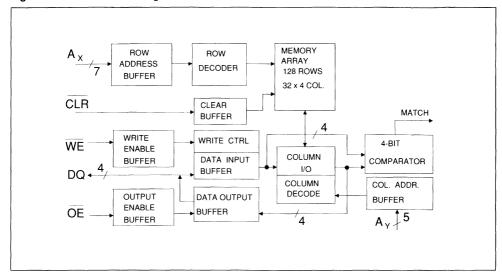

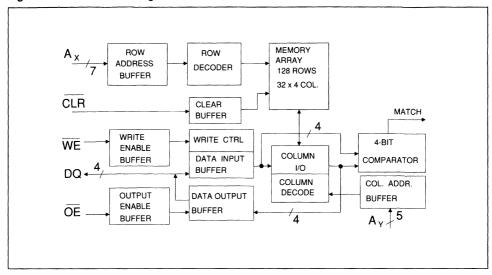

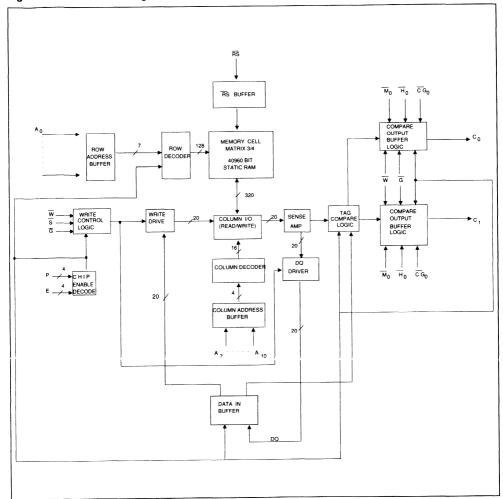

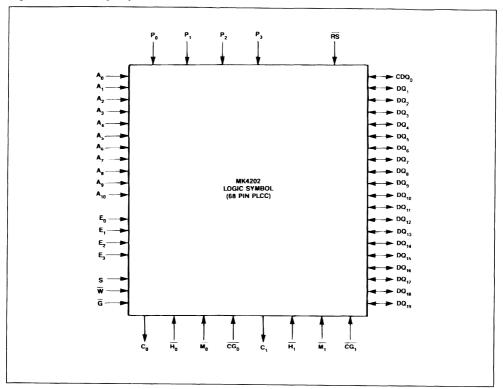

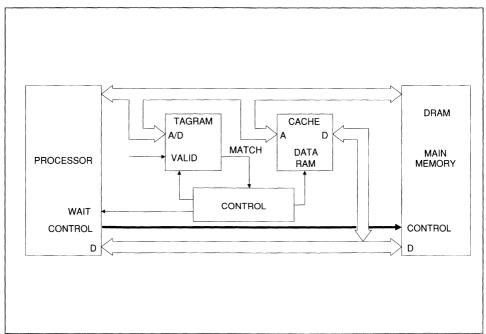

- \* The Cache-Tag family consists of devices, like very fast SRAMs with on board comparators, called TAGRAMs. A TAGRAM™ is that part of a cache subsystem that determines if data or instructions is retained in the cache memory (data cache). SGS-THOMSON offers various organizations x4, x8 and x20 and speed as fast as 12ns.

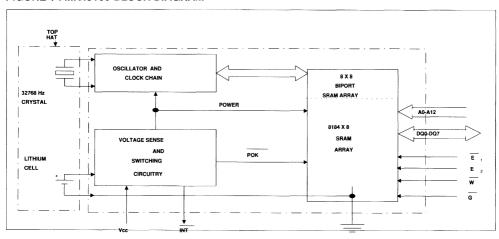

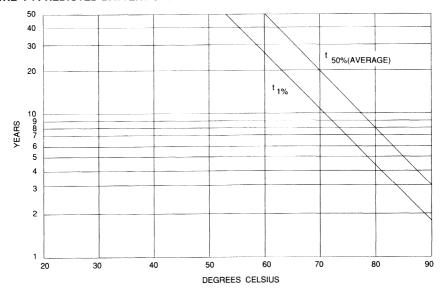

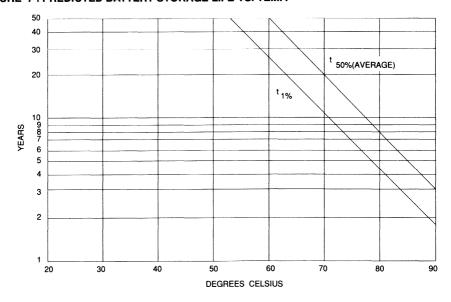

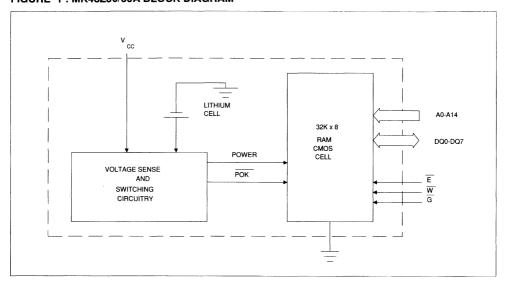

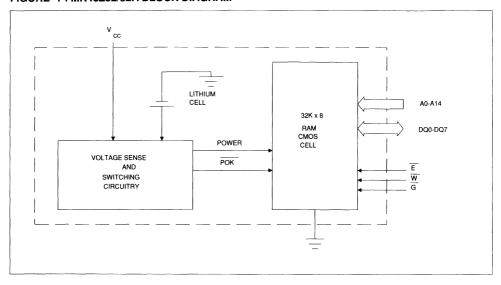

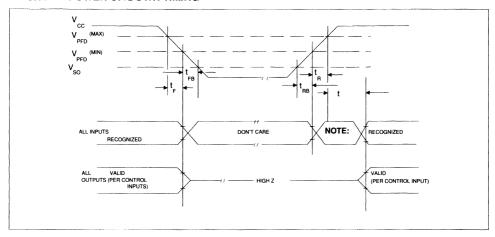

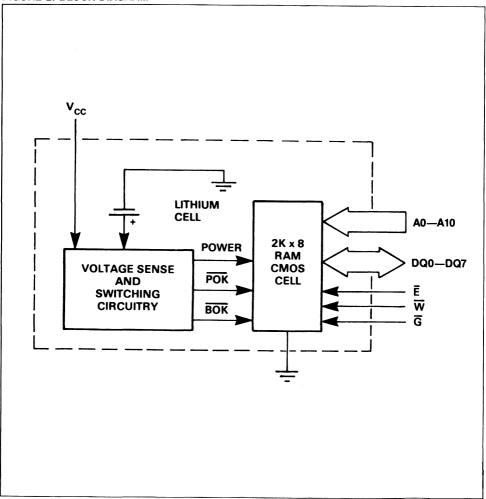

- \* The Zeropower<sup>TM</sup> and Timekeeper<sup>TM</sup> RAM family combines the operating simplicity of conventional byte-wide SRAMs with the excellent data integrity of Zeropower<sup>TM</sup> technology. This integrity is achieved, thanks to the use of advanced CMOS technology and long-life lithium cells. With density from 2k x 8 to 32k x 8 and access/cycle from 55ns to 200ns, SGS-THOMSON covers the full range of non-volatile needs for all microprocessor based systems. Thanks to the combined features of Zeropower<sup>TM</sup> technology with an on chip real-time clock, Timekeeper<sup>TM</sup>. RAM offer unparalleled non-volatile performances while maintaining standard pin-out. Applications include RAM clock/timer for communication, industrial systems, PCs, workstations.

### PRODUCTION

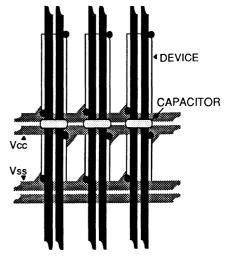

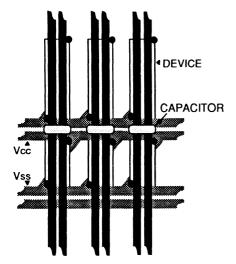

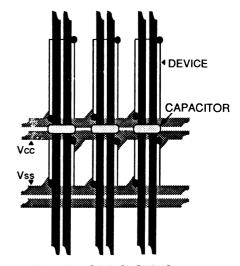

There are two facilities which presently manufacture the SRAM product line, Newport (UK) and Carrollton (USA). The Newport facility is an 8000 square meter building with a 3000 square meter clean room operating to Class 10 environment in the work areas. The facility operates a 4" wafer line and has the capacity to upgrade to a 6" sub micron capability. The Carrollton facility has a 5000 square meter class 100 4" wafer line and a 700 square meter class 10 6" wafer line with sub-micron capability. Additional manufacturing capacity is available in Rousset, France where both a 4 and 5" line are in operation.

Advanced manufacturing equipment is used in these facilities to produce high performance devices, some consisting of up to one million transistors. Wafer steppers, plasma etchers and ion implanters form the basis of fabrication.

SGS-THOMSON Muar (Malaysia) is the main in-house assembly facility for SRAM.

The in-house facilities used for final SRAM testing are located in Newport (UK), Colorado Springs (USA), Toa Payoh (Singapore) and Muar (Malaysia).

### **INTRODUCTION**

Carrolton, TX (USA)

Newport (UK)

### INTRODUCTION

### **MILITARY**

Many of our static RAMs are available in military versions processed in full compliance with MIL-STD-883C. Additionally, several JAN qualified devices are available for some of the product lines.

We also supports the US Government Defense Electronics Supply Center (DESC) Standard Military Drawing (SMD) program and is an approved supplier of a range of the SMDs already established by DESC.

### **FUTURE DEVELOPMENTS**

Research and Development

The SGS-THOMSON Group has achieved technical success based on a position of leadership in products and process technology in conjunction with substantial R&D investment which, in 1988, represented 20 percent of sales, well above the estimated worldwide average of 13 percent for the top 10 semiconductor manufacturers.

Process Developments

New process technologies are continuing to be developed for next generation products. Work is taking place now to scale present technologies while new sub micron CMOS technologies are being brought into production.

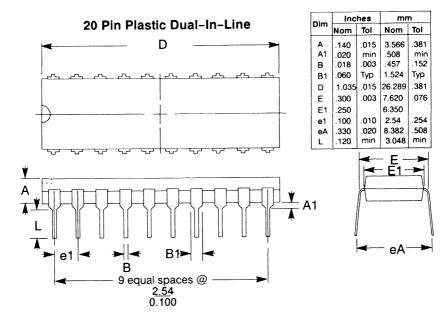

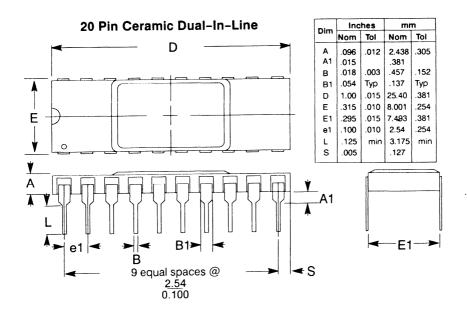

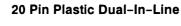

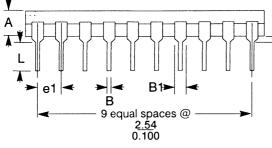

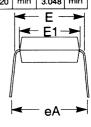

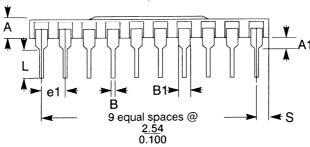

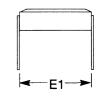

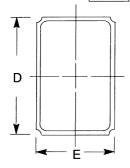

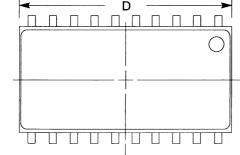

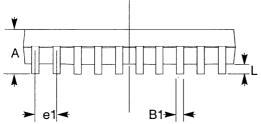

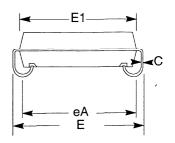

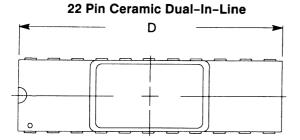

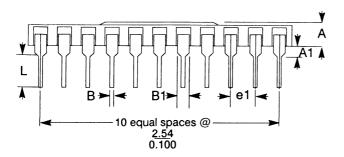

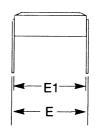

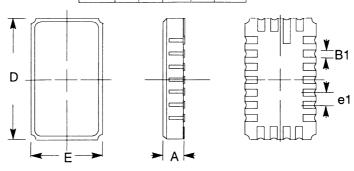

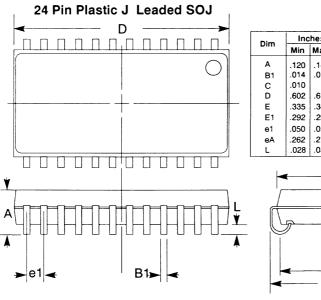

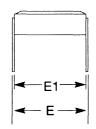

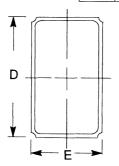

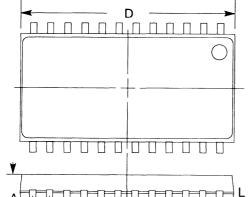

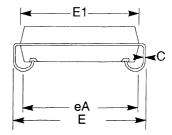

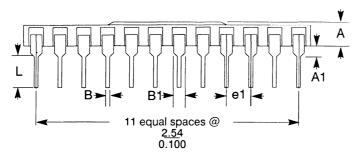

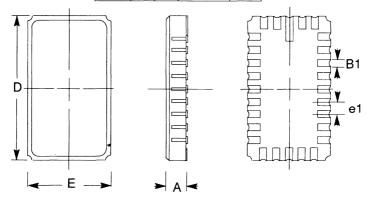

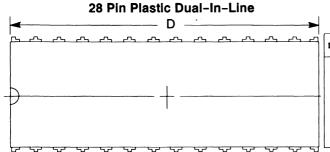

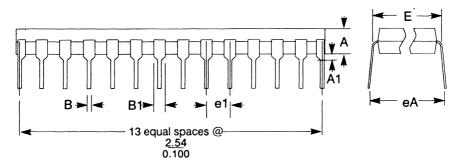

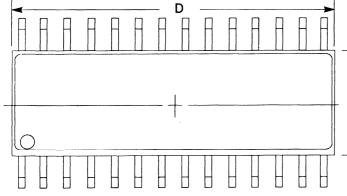

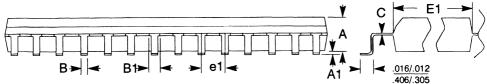

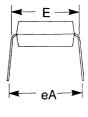

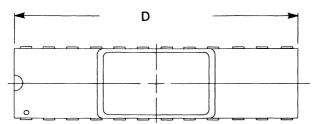

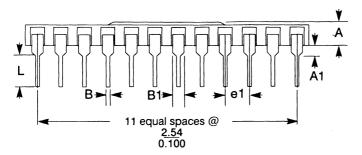

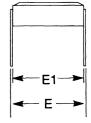

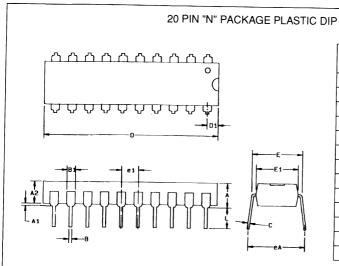

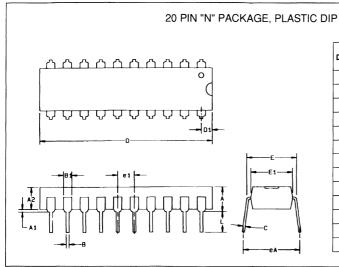

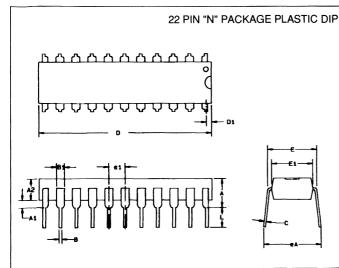

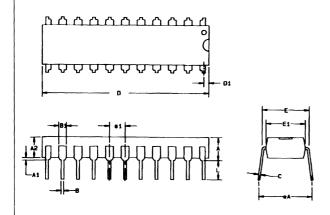

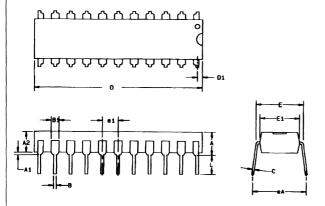

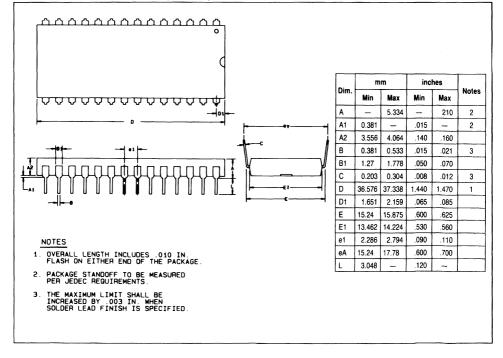

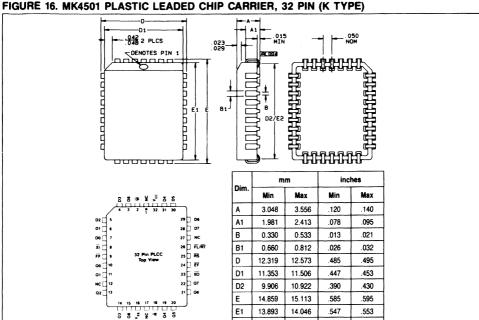

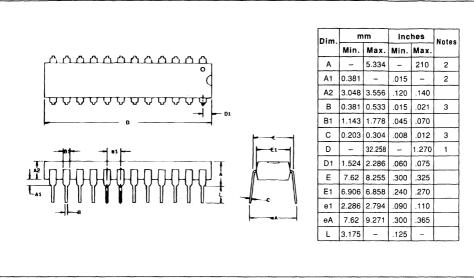

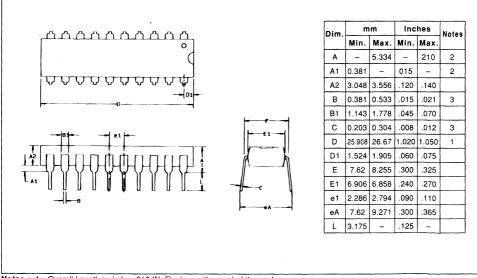

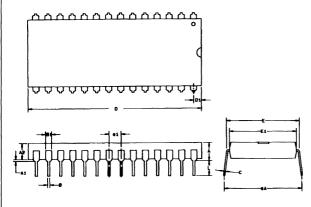

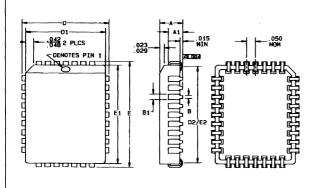

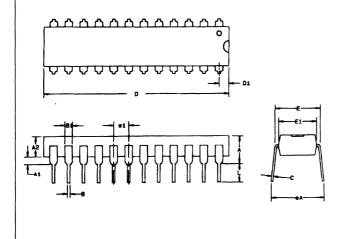

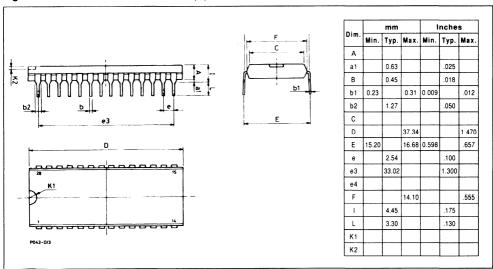

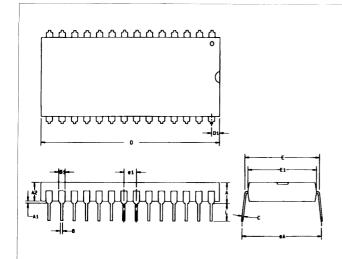

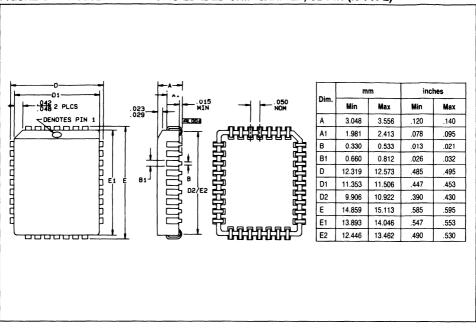

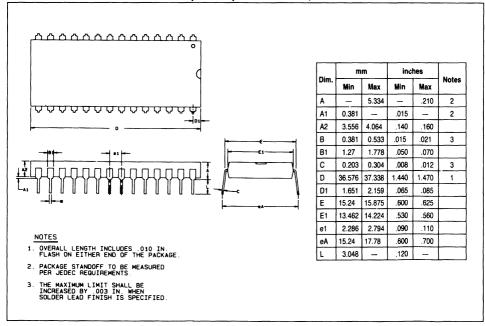

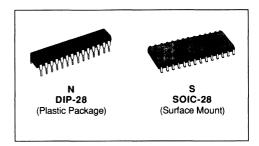

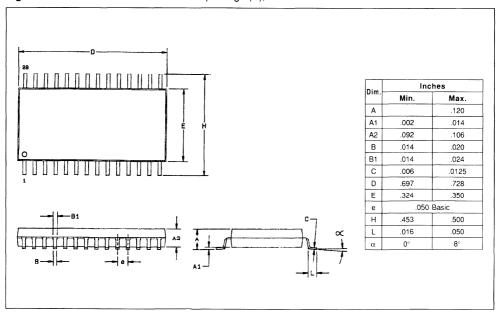

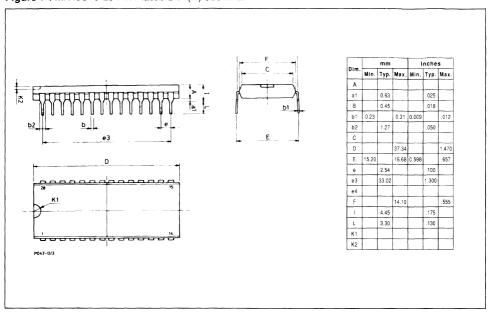

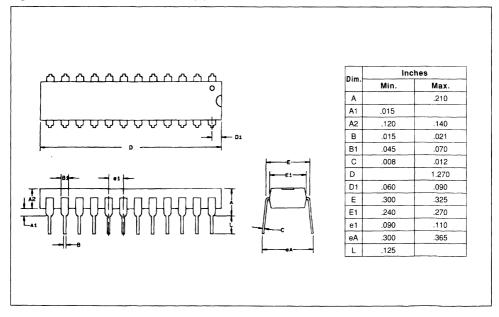

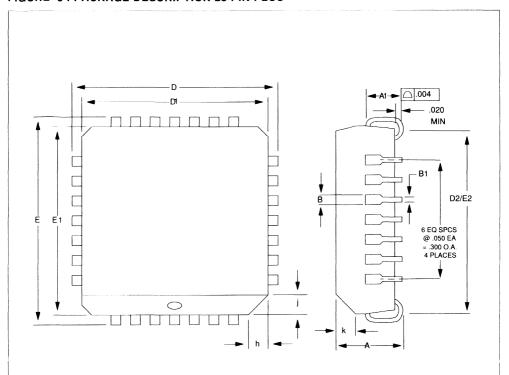

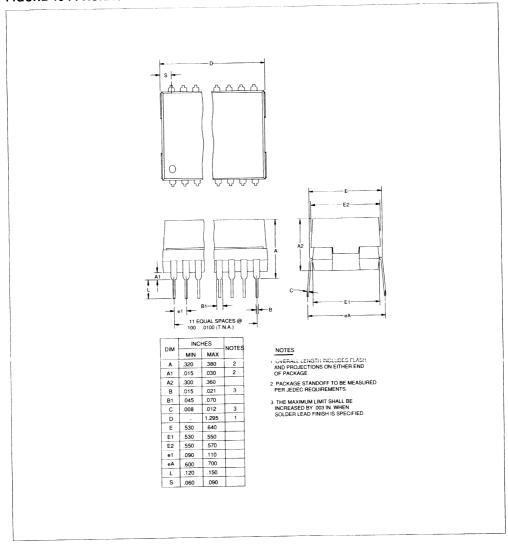

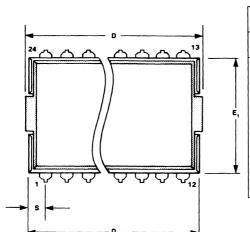

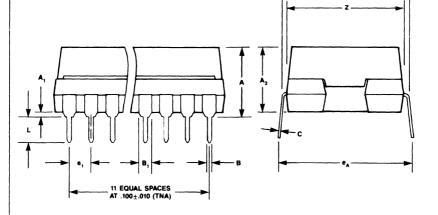

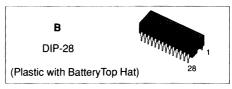

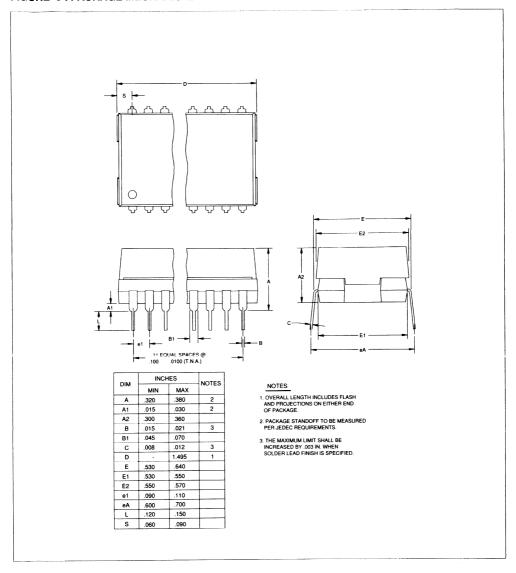

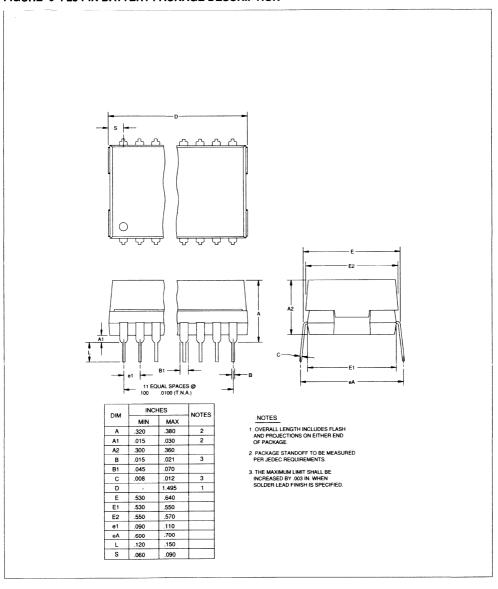

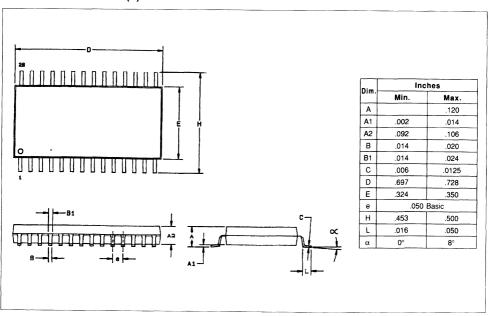

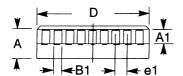

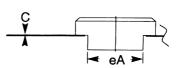

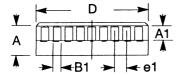

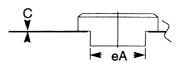

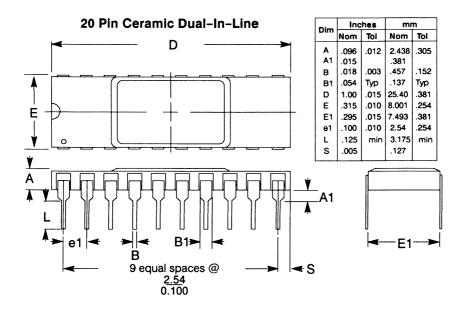

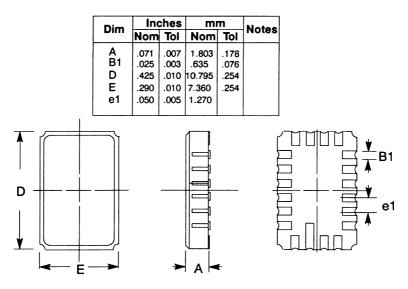

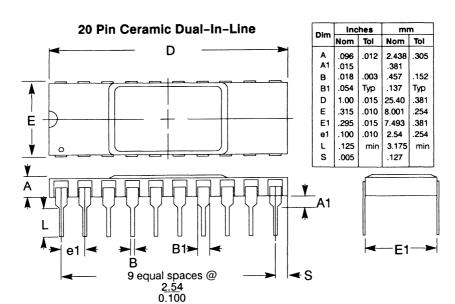

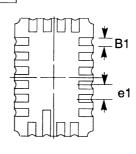

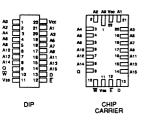

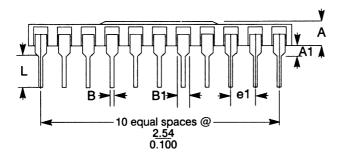

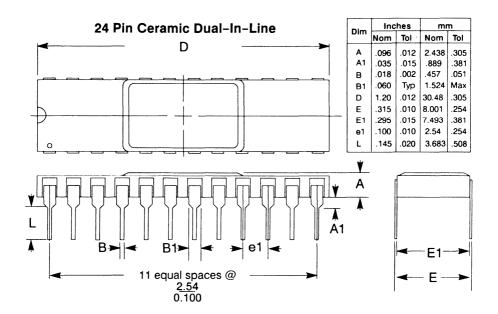

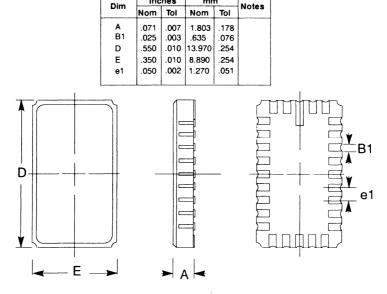

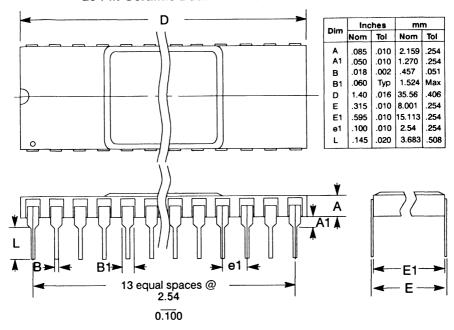

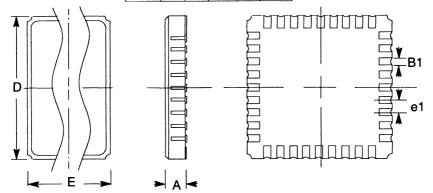

Package Developments

A wide selection of packages are available including plastic and ceramic DIP. Where surface mount technology is desirable, the package offerings include PLCC, LCC, SOIC, SOJ, and Flat-pack. Refer to the individual datasheets for a listing of the packages available for a particular device.

### INTRODUCTION

The Quality and Reliability of a product depend on all the activities from the conception and design of a new product, through production and shipment, to the service given to the customers.

It is well known that Reliability must be designed into the product and the process. To manufacture consistently reliable high quality products, SGS-THOMSON Microelectronics believes that it is essential for everyone in the Group to appreciate the importance of maintaining and improving the levels of Quality and Reliability.

SGS-THOMSON has adopted a Total Quality Control approach which means that everyone in the Group must work to improve Quality.

With this approach problems can be solved at the stage where they arise, so that latent failures are not carried over to the next stage or to the finished product. Total Quality Control assures the conditions to avoid quality problems rather than simply eliminating defective finished products.

The following information describes in a precis form the SGS-THOMSON approach to Quality and Reliability. The subject is comprehensively detailed in the SGS-THOMSON Quality and Reliability publication SURE 5. This program is also applied totally to INMOS products.

### **QUALITY CULTURE**

It is the precise choice of SGS-THOMSON to win its customers' trust via the establishment of a position of leadership for Service and Quality. The Group must therefore have a quality based culture.

This culture can be seen in the behavior of every person within the Group and in the way each person interacts with his or her fellow worker to establish new and ever more demanding goals. It is sustained and nurtured through well defined policies, procedures, training and, of paramount importance, through examples from the very highest Group management levels.

That quality is perceived as a company wide responsibility is no more obvious than in the field of training. An ongoing program called Total Quality Control, was begun in 1982 to improve all people and departments in the Group wherever the Group operates throughout the world.

Total Quality Control takes the position that it is not enough to believe that things must be done, you must be able to do them. To this end it has as its primary objectives:

- \* Promotion of the Total Quality Control concept

- \* Training on statistical tools for people from all departments

- \* The creation of technical work groups for specific quality improvement programs

- \* The introduction of Quality Circles

Fundamental to this program is the conviction that quality is not an option, it is an obligation and that everyone in the Group can, given suitable motivation and training, make a real contribution to overall improvements in quality levels.

From the very highest management levels and involving designers, engineers, production, supervisors and line operators in addition to Quality and Reliability people, the Total Quality Control program is focused on:

- \* Personal motivation

- \* Quality in design

- Reliability in design

- \* Improved Statistical Process Control

- \* Customer satisfaction

In addition quality circles have been set up within the Group. The first, in 1982, was in the Group's Far East factories, with the first Quality Circle Convention being held in Singapore on January 30th 1983.

Recently SGS-THOMSON has begun a new company wide campaign - Quality and Service Culture for Excellence - based on the premise that basic quality ideas and methodology, if applied properly, will give:

- \* Complete Customer satisfaction

- \* Zero defect products

- \* Minimum product costs

These three basic ingredients for excellence will be complemented by a long term program to improve data processing networks and to reduce response times at all levels as well as the localization of everyone's efforts on service, on quality and on process stability.

Our ultimate goal is to supply the products requested by our customers with zero delinquency, zero defects and of course "just in time".

### ORGANIZATION AND MANAGEMENT

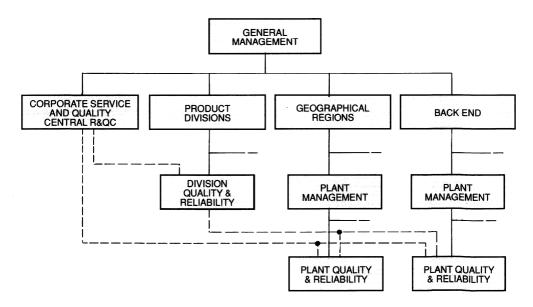

SGS-THOMSON is organized in product divisions, geographical sales areas (Regions) and Corporate departments.

Quality and Reliability control activities are managed, performed and promoted by the Corporate Service and Quality group (which reports to the top management) and Quality and Reliability departments at division and plant levels.

Part of Corporate Service and Quality group is the Central Reliability and Quality Control department. This organization makes it possible for SGS-THOMSON to handle Quality and Reliability for an extensive product range both effectively and efficiently.

Education and training programs in the field of Excellence and Quality are managed by the Corporate Service and Quality organization in cooperation with Human Resources department.

At every production location there is an incoming inspection department with the job of assuring the quality of purchased materials.

Division Q&R departments evaluate the reliability of new processes and new products, before they go into volume production.

They require and coordinate corrective actions necessary to improve Q&R of products and processes; these improvements are planned in quality budgets.

They perform and collect reliability results and issue reliability reports for their products.

Division Q&R departments interface directly with customers from design phase to approval of customers' product specifications.

In the past, successful in-house customer qualification, testing and joint qualification programs with customers has been achieved. SGS-THOMSON remains committed to these joint customer/vendor programs.

Plant Q&R departments perform all Quality and Reliability inspections and controls relevant to production done in their plants such as: incoming inspection, in process control, outgoing inspection, reliability testing and failure analysis.

### **QUALITY BY DESIGN**

Since the Quality and Reliability of semiconductor devices depend to a large extent on the basic structure, SGS-THOMSON pays careful attention to Q&R studies at the design stage, paying deep attention to user's reliability requirements and operating conditions. Quality and Reliability checkpoints for materials, process and device structure are considered from the design phase on.

One of the key steps in the Design Review which consists of a study of design documents, the definition of reliability test methods to check on the compatibility of processes with design goals and conditions of use, and review of failure mechanism history in similar products.

In addition, qualification procedures are used mainly to ascertain the main characteristics of new processes/products (or to evaluate process/product changes) and to guarantee the availability of a characterization and the complete set of specifications for introduction to SGS-THOMSON manufacturing. Qualification should demonstrate capability to meet customer requirements.

### QUALITY AUDITING

SGS-THOMSON performs quality audits to verify that products, processes, programs and the Quality and Reliability organizations are still in accordance with the written procedures and specifications.

A quality audit does not replace the normal quality monitors or acceptance but helps to ensure that everything is being done as it should be and to anticipate quality problems.

SGS-THOMSON factories are familiar with internal and external audits.

### THE SPECIFICATION SYSTEM

Quality and Reliability are measurable features. But, for measurements to have any meaning, they must be carried out in accordance with strict procedures and methods. Similarly production processes must be managed in a repeatable way. This means that detailed instructions and descriptions of every process step must be prepared and kept updated.

This information is formalized in the Group's specifications that cover all the procedures and process instructions. This the Specification System documents all the various manufacturing processes and encompasses the SGS-THOMSON technical know-how.

The Specification System consists of a series of documents properly organized by subject and content. The system is managed and administered by Document Control at Divisional Specification Centres for efficiently issuing, updating, approving and distributing specifications to all the relevant departments. Special text processing software is used to ensure rapid updating and distribution of specification documents. The Specification Centres guarantee homogeneity in specifications, record changes histories and issues general specification procedures.

A very strict Group procedure governs the engineering changes (issue, approval and modifications).

### **RELIABILITY ASSURANCE**

Reliability testing is an ongoing process adopted to identify and then improve reliability performance.

Accelerated tests, such as extended temperature operating life, THB and temperature cycling, are important tools for evaluating long-term reliability and stability of process and product parameters.

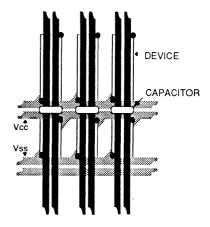

MOS device life test equipment

SGS-THOMSON also performs rigorous tests throughout production to ensure that production devices have the properly designed reliability.

Reliability tests are conducted in two stages:

first we test our engineering samples during design and development stages to see if their Q&R corresponds to that called for in the design. Reliability testing is usually performed on a small sample but for long periods or under very accelerated conditions to investigate wear out failures and to determine tolerances and limits of design. For these tests it is also possible to use the step-stress procedure (eg ESD resistance evaluation);

the second type of test is performed periodically during production to check, maintain and improve the assured Quality and Reliability levels.

The reliability tests involve both environmental and endurance examination and are performed under conditions more severe than those met in the field. These conditions are chosen to accelerate the occurrence of failures that would appear in actual operation, and care is taken to ensure that the failure modes and mechanisms are unchanged. The data from reliability tests provide an objective tool for product performance evaluation under a wide range of conditions.

When a failure occurs, the SGS-THOMSON engineers conduct an in-depth analysis of the failure mechanism/mode to apply immediate suitable corrective actions.

Reliability testing activity during recent years has been extended to all SGS-THOMSON factories with new and advanced equipment enabling all the plants to perform all the main tests.

### **MILITARY QUALIFICATION**

### **MILITARY PRODUCT PROGRAM**

A Military Product Program has been developed to meet the increasingly demanding requirements for Class B memory product in accordance with paragraph 1.2.1 of MIL-STD-883 "Provisions for the use of MIL-STD-883 in conjunction with non-JAN devices".

Our MIL-STD-883 Class B product is screened to the specifications of Method 5004 with electrical testing executed over the military temperature range -55 C to + 125 C.

Each inspection lot is subjected to the requirements of method 5004 Group A Electrical sampling and Group B Mechanical and Environmental sample testing. Additionally, all new product and changes to product as defined in MIL-M-38510 paragraph 3.4.2 (major changes) is qualified per method 5005 Group C

(Die related) and Group D (Package related tests). Periodic Conformance Testing is carried out per the requirements of MIL-STD-883 paragraph 1.2.1 for all relevant die families and package types.

Full details of our military processing are included in a "General Military Processing Specification", which may be obtained upon request.

Suitability for use in specific applications should be determined by using the guidelines of MIL-STD-454.

By specifying one of our military products, the user is assured of a product which has been subjected to the full Screening and Quality Conformance requirements of paragraph 1.2.1 of MIL-STD-883 in addition to the full range of in-house process, test and quality control functions designed to enhance the quality and reliability of all products.

### STANDARD MILITARY DRAWING PROGRAM

The in-house Standard Military Drawing (SMD) program was introduced in 1986 to supply military and governmental products. The SMD Program was implemented by the US Government and its associated subcontractors to provide the industry with a single SMD for each military IC requirement. These SMDs are intended to replace the multiplicity of Source Control Drawings (SCDs) generated by each contractor. Components specified according to the SMD Program are standard military MIL-STD-883 compliant devices.

SGS-THOMSON and other IC manufacturers, initiate the development of SMDs in conjunction with military contractors who have significant demand for the particular device. Together they initiate an SMD proposal which the Defense Electronics Supply Center (DESC) screens and approves. Accepted SMDs are then circulated by DESC to industry vendors and consumers to obtain multiple sources and registered users.

The SGS-THOMSON Group fully supports the Standard Military Drawing Program and the DESC efforts to expand its usage.

Refer to the cross reference information which lists each approved product by its SMD number and the corresponding part number

### **ALPHANUMERICAL INDEX**

(unless otherwise specified all Static RAMs listed are produced in CMOS technology)

| Part Number      | Organization        | Description                                                                       | Page Number |

|------------------|---------------------|-----------------------------------------------------------------------------------|-------------|

| IMS1203          | 4Kx1                | SRAM                                                                              | 31          |

| IMS1203M         | 4Kx1                | Military SRAM                                                                     | 501         |

| IMS1223          | 1Kx4                | SRAM                                                                              | 39          |

| IMS1223M         | 1Kx4                | Military SRAM                                                                     | 511         |

| IMS1400M         | 16Kx1               | NMOŚ Military SRAM                                                                | 521         |

| IMS1403          | 16Kx1               | SRAM                                                                              | 47          |

| IMS1403M/LM      | 16Kx1               | Military SRAM                                                                     | 531         |

| IMS1420M         | 4Kx4                | Military SRAM                                                                     | 541         |

| IMS1423          | 4Kx4                | SRAM                                                                              | 57          |

| IMS1423M         | 4Kx4                | Military SRAM                                                                     | 551         |

| IMS1600/1601L    | 64Kx1               | SRAM                                                                              | 67          |

| IMS1600M/1601LM  | 64Kx1               | Military SRAM                                                                     | 561         |

| IMS1620          | 16Kx4               | SRAM                                                                              | 77          |

| IMS1620M/LM      | 16Kx4               | Militan CDAM                                                                      | 571         |

| IMS1624          | 16Kx4               | Military SRAM                                                                     | 87          |

|                  |                     | Military CDAM with OF                                                             |             |

| IMS1624M/LM      | 16Kx4               | Military SRAM with OE                                                             | 581         |

| IMS1630L         | 8Kx8                | SRAM with OE                                                                      | 97          |

| IMS1630M/LM      | 8Kx8                | Military SRAM                                                                     | 591         |

| IMS16X5          | (64K)               | Very High Speed Family SRAM                                                       | 107         |

| IMS16X5M         | (64K)               | Very High Speed Family Military SRAM                                              | 601         |

| IMS1800          | 256Kx1              | SRAM                                                                              | 119         |

| IMS1800M         | 256Kx1              | Military SRAM                                                                     | 603         |

| IMS1820          | 64Kx4               | SRAM                                                                              | 129         |

| IMS1820M         | 64Kx4               | Military SRAM                                                                     | 605         |

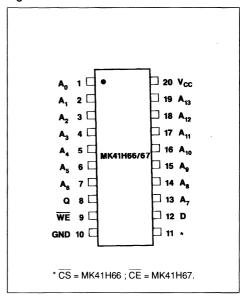

| MK41H66/H67      | 16Kx1               | SRAM                                                                              | 139         |

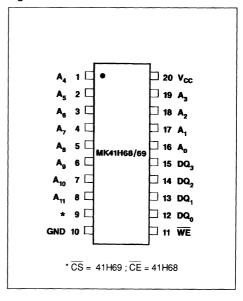

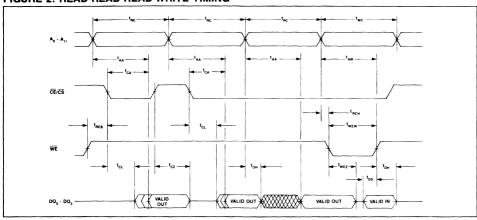

| MK41H68/69       | 4Kx4                | SRAM                                                                              | 149         |

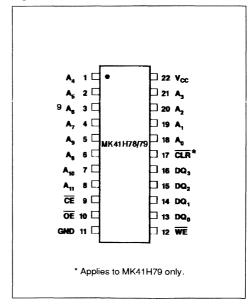

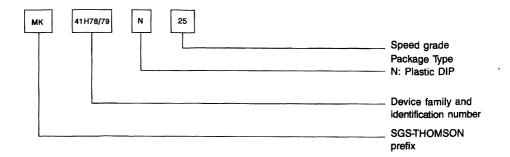

| MK41H78/79       | 4Kx4                | SRAM with OE and flash clear                                                      | 159         |

| MK41H80          | 4Kx4                | Cache Tag                                                                         | 171         |

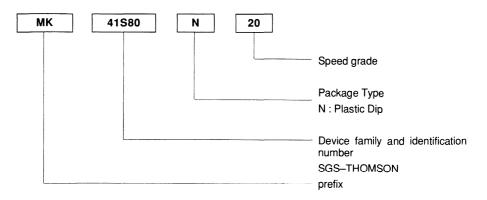

| MK41S80          | 4Kx4                | Very high speed Cache Tag                                                         | 183         |

| MK4202           | 2Kx20               | Cache Tag                                                                         | 195         |

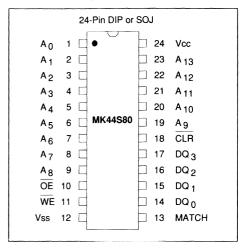

| MK44S80          | 16Kx4               | Cache Tag                                                                         | 215         |

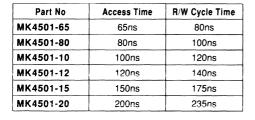

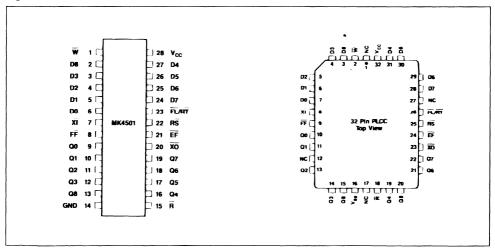

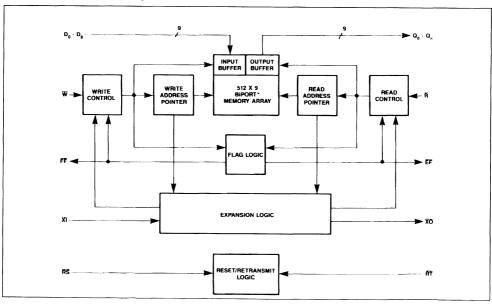

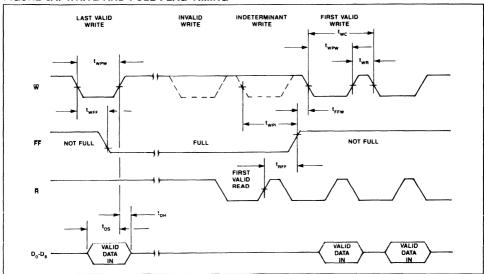

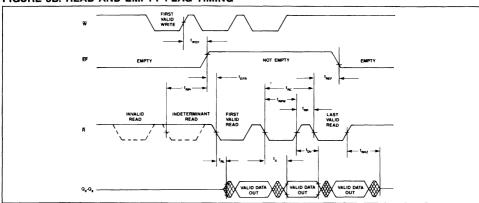

| MK4501           | 512x9               | FIFO                                                                              | 217         |

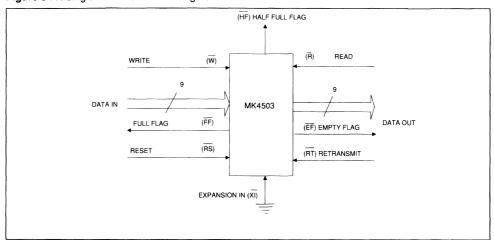

| MK4503           | 2048x9              | FIFO                                                                              | 233         |

| MK4505           | 1024x5              | Clocked FIFO                                                                      | 251         |

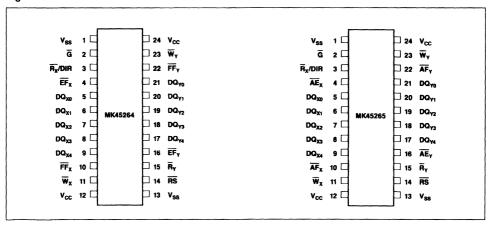

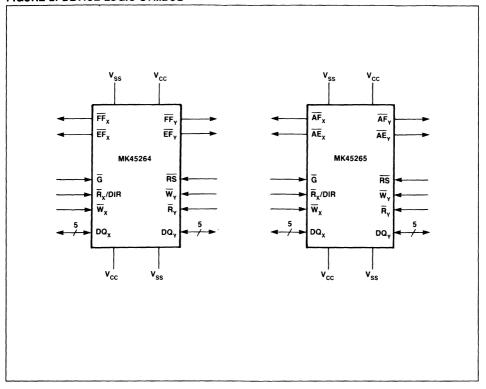

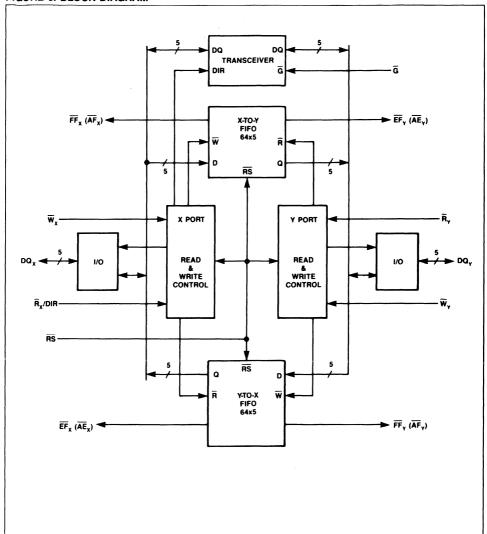

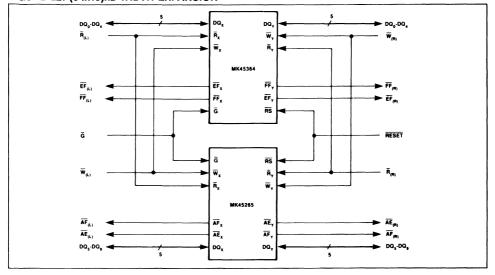

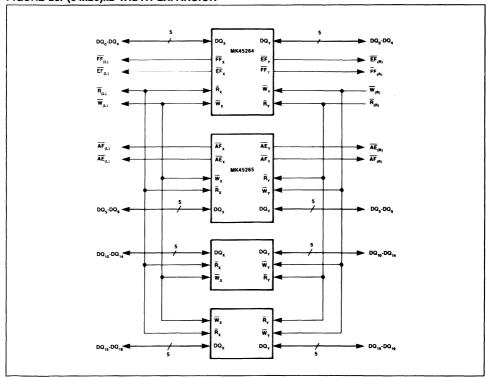

| MK45264/265      | 64x5X2              | FIFO                                                                              | 271         |

| MK45H01/02/03    | 512x9/1024x9/2048X9 | High speed FIFOs                                                                  | 289         |

| MK45H04/08       | 4Kx9/8Kx9           | High speed FIFOs                                                                  | 307         |

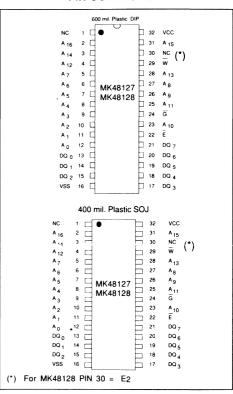

| MK48127/28       | 128Kx8              | SŘAM                                                                              | 323         |

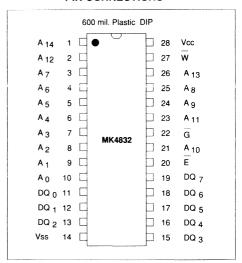

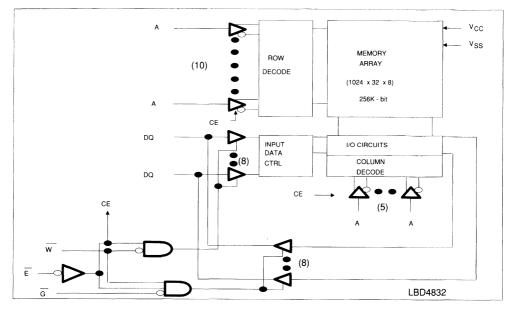

| MK4832           | 32Kx8               | SRAM                                                                              | 325         |

| MK48C02          | 2Kx8                | Zeropower without battery                                                         | 335         |

| MK48H64          | 8Kx8                | SRAM                                                                              | 345         |

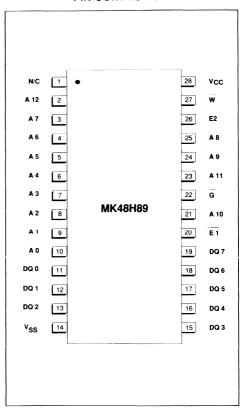

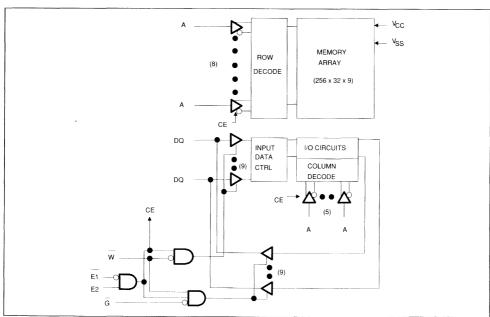

| MK48H89          | 8Kx9                | SRAM                                                                              | 355         |

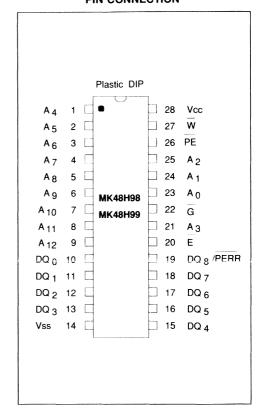

| MK48H98/99       | 8Kx8/9              | SRAM with parity                                                                  | 357         |

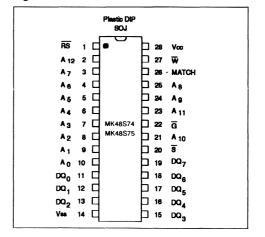

| MK48S74/75       | 8Kx8                | Cache Tag                                                                         | 361         |

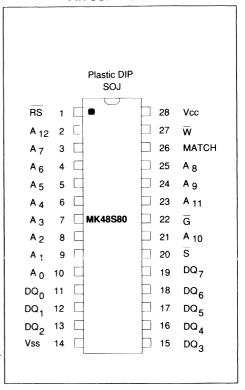

| MK48S80          | 8Kx8                | Cache Tag                                                                         | 373         |

| MK48T02/12       | 2Kx8                | Timekeeper                                                                        | 375<br>375  |

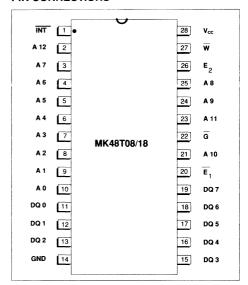

| MK48T08/18       | 8Kx8                | Timekeeper                                                                        | 389         |

| MK48T85Q         | 0.00                | Address/data multiplexed real-time clock                                          | 403         |

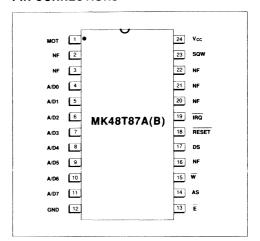

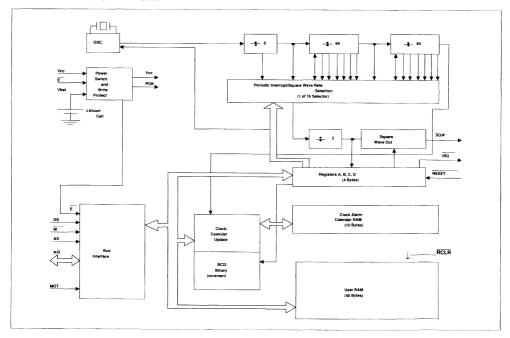

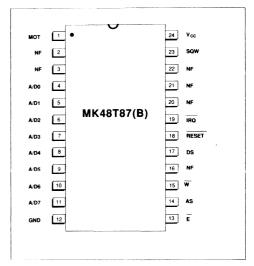

| MK48T87/87A/B    |                     | Address/data multiplexed real-time clock                                          | 403<br>409  |

| MK48T87B         |                     | Address/data multiplexed real-time clock Address/data multiplexed real-time clock | 411         |

| MK48Z02/12       | 2Kx8                | Zeropower                                                                         | 431         |

|                  | 8Kx8                | Zeropower                                                                         |             |

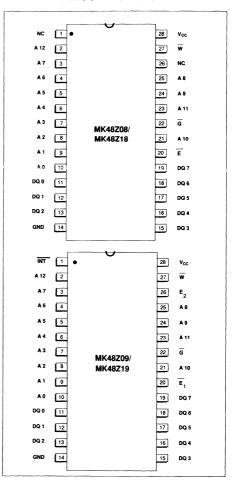

| MK48Z08/09/18/19 |                     | Zeropower                                                                         | 443<br>457  |

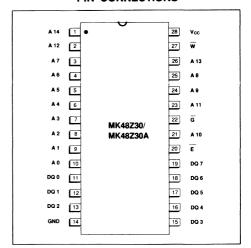

| MK48Z30/Z30A     | 32Kx8               | Zeropower                                                                         | 457         |

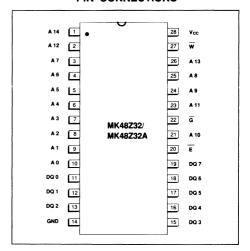

| MK48Z32/Z32A     | 32Kx8               | Zeropower                                                                         | 469         |

| MK6116/MKI6116   | 2Kx8                | SRAM                                                                              | 479         |

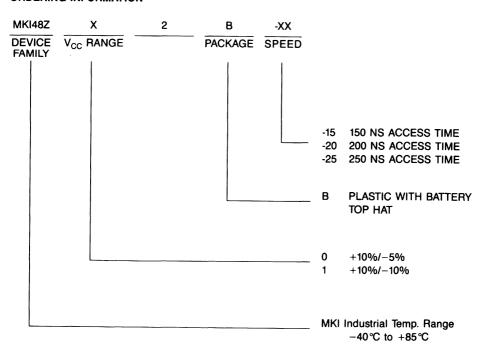

| MKI48Z02/12      | 2Kx8                | Zeropower Industrial temp.range                                                   | 489         |

# **PRODUCT GUIDE**

| , |  |  |

|---|--|--|

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

|   |  |  |

### **ZEROPOWERS**

| ORGANISATION              | PART       |                    |                 | ICCma       |              |                | TEMP           |          |

|---------------------------|------------|--------------------|-----------------|-------------|--------------|----------------|----------------|----------|

| DESCRIPTION               | NUMBER     | SPEEDns            | ACTIVE<br>mA@ns | TTL<br>STBY | CMOS<br>STBY | vcc            | RANGE          | PACKAGE  |

| – 2KX8                    | MK48Z02    | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 5%   | 0 to + 70°C    | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED    | MK48Z02BU  | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 5%   | 0 to + 70°C    | P DIP 24 |

| – 2K 8                    | MK48Z12    | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED    | MK48Z12BU  | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 24 |

| - 2KX8                    | MKI48Z02   | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 5%   | - 40 to + 85°C | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED    | MKI48Z02BU | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 5%   | - 40 to + 85°C | P DIP 24 |

| – 2KX8                    | MKI48Z12   | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 10%  | - 40 to + 85°C | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED    | MKI48Z12BU | 120, 150, 200, 250 | 90              | 3           | 1            | 5V + 10 - 10%  | - 40 to + 85°C | P DIP 24 |

| – 2KX8<br>W/O BATTERY     | MK48C02AN  | 150, 200, 250      | 90              | 3           | 1            | 5V + 10 - 5%   | 0 to + 70°C    | P DIP 24 |

| – 2KX8<br>W/O BATTERY     | MK48C02AK  | 150, 200, 250      | 90              | 3           | 1            | 5V + 10 - 5%   | 0 to + 70°C    | PLCC 32  |

| – 8KX8                    | MK48Z08    | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| UL-CERTIFIED              |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| - 8KX8                    | MK48Z08BU  | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| UL-CERTIFIED              |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| – 8KX8                    | MK48Z18    | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

|                           |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| - 8KX8                    | MK48Z18BU  | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| UL-CERTIFIED              |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| – 8KX8                    | MK48Z09    | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| PWR FAIL INT              |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| - 8KX8<br>UL-CERTIFIED    | MK48Z09BU  | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| PWR FAIL INT              |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| - 8KX8                    | MK48Z19    | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| PWR FAIL INT              | IVIN40Z13  | 100, 150, 200      | 80@100          |             | 3            | 30 + 10 - 1078 | 0.0 + 70 0     | 1 Dil 20 |

| - 8KX8<br>UL-CERTIFIED    | MK48Z19BU  | 55,70              | 125@70          | 3           | 3            | 5V + 10 - 10%  | 0 to + 70°C    | P DIP 28 |

| PWR FAIL INT              |            | 100, 150, 200      | 80@100          |             |              |                |                |          |

| - 32KX8<br>10 YEARS -25°C | MK48Z30    | 100, 120, 150      | 90              | 5           | 2            | 5V + 10 - 5%   | 0 to + 70°C    | P DIP 28 |

| - 32KX8<br>10 YEARS -25°C | MK48Z30A   | 100, 120, 150      | 90              | 5           | 2            | 5V + 10 - 5%   | 0 to + 70°C    | P DIP 28 |

| - 32KX8<br>10 YEARS -70°C | MK48Z32    | 100, 120, 150      | 90              | 5           | 2            | 5V + 10 - 5%   | 0 to + 70°C    | P DIP 28 |

### **SELECTION GUIDE**

### **TIMEKEEPERS**

| ORGANISATION                             | PART        |                    |                 | ICCma       |              |                  | TEMP         |          |

|------------------------------------------|-------------|--------------------|-----------------|-------------|--------------|------------------|--------------|----------|

| DESCRIPTION                              | NUMBER      | SPEEDns            | ACTIVE<br>mA@ns | TTL<br>STBY | CMOS<br>STBY | vcc              | RANGE        | PACKAGE  |

| – 2KX8                                   | MK48T02     | 120, 150, 200, 250 | 80              | 5           | 3            | 5V + 10 - 5%     | 0 to + 70°C  | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED                   | MK48T02BU   | 120, 150, 200, 250 | 80              | 5           | 3            | 5V + 10 - 5%     | 0 to + 70°C  | P DIP 24 |

| – 2KX8                                   | MK48T12     | 120, 150, 200, 250 | 80              | 5           | 3            | 5V + 10 - 10%    | 0 to + 70°C  | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED                   | MK48T12BU   | 150, 200, 250      | 80              | 5           | 3            | 5V + 10 - 10%    | 0 to + 70°C  | P DIP 24 |

| - 2KX8                                   | MKI48T02    | 120, 150, 200, 250 | 80              | 5           | 3            | 5V + 10 - 5%     | -40 to +85°C | P DIP 24 |

| – 2KX8<br>UL-CERTIFIED                   | MKI48T02BU  | 120, 150, 200, 250 | 80              | 5           | 3            | 5V + 10 - 10%    | -40 to +85°C | P DIP 24 |

| - 8KX8                                   | MK48T08     | 100, 150, 200      | 80              | 3           | 3            | 5V + 10 -5%      | 0 to + 70°C  | P DIP 24 |

| - 8KX8                                   | MK48T18     | 100, 150, 200      | 80              | 3           | 3            | 5V + 10-10%      | 0 to + 70°C  | P DIP 24 |

| - PC<br>REAL TIME<br>CLOCK               | MK48T87/87A | 100                | 15              | NA          | NA           | 5V + 10 -<br>10% | 0 to + 70°C  | P DIP 24 |

| -PC<br>REAL TIME<br>CLOCK<br>W/O BATTERY | MK48T85Q    | 100                | 15              | 0,5         | NA           | 5V + 10 - 10%    | 0 to + 70°C  | PLCC 28  |

### **CACHETAG MEMORIES**

| ORGANISATION              | PART    |               |                 | ICCma       |              |               | TEMP        |                     |

|---------------------------|---------|---------------|-----------------|-------------|--------------|---------------|-------------|---------------------|

| DESCRIPTION               | NUMBER  | SPEEDns       | ACTIVE<br>mA@ns | TTL<br>STBY | CMOS<br>STBY | vcc           | RANGE       | PACKAGE             |

| – 4KX4                    | MK41H80 | 20,22, 25, 35 | 120             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 22            |

| – 4KX4                    | MK41S80 | 12, 15        | 120             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 22<br>/SOJ 24 |

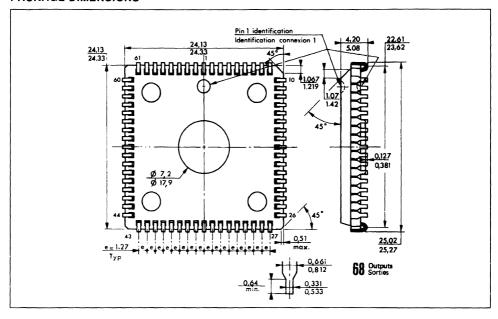

| - 2KX20                   | MK4202  | 20, 22, 25    | 250             | 50          | NA           | 5V + 10 - 10% | 0 to + 70°C | PLCC 68             |

| - 8KX8                    | MK48S74 | 20, 22, 25    | 150             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28<br>/SOJ 28 |

| 8KX8<br>Totem Pole Output | MK48S80 | 20, 22, 25    | 150             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28<br>/SOJ 28 |

| 16KX4                     | MK44S80 | 15, 17, 20    | 150             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 24<br>300 MIL |

### FIFO's

| ORGANISATION    | PART     |                               |                 | ICCma       |              |               | TEMP        |                         |

|-----------------|----------|-------------------------------|-----------------|-------------|--------------|---------------|-------------|-------------------------|

| DESCRIPTION     | NUMBER   | SPEEDns                       | ACTIVE<br>mA@ns | TTL<br>STBY | CMOS<br>STBY | vcc           | RANGE       | PACKAGE                 |

| - 512X9         | MK4501   | 65, 80, 100, 120<br>150 & 200 | 80              | 8           | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28<br>/PLCC 32    |

| - 512X9 FAST    | MK45H01  | 25, 35, 50, 65, 120           | 120             | 12          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28(1)<br>/PLCC 32 |

| - 1KX9 FAST     | MK45H02  | 25, 35, 50, 65, 120           | 120             | 12          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28(1)<br>/PLCC 32 |

| – 2KX9          | MK4503   | 65, 80, 100, 120<br>150 & 200 | 120             | 12          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28<br>/PLCC 32    |

| - 2KX9 FAST     | MK45H03  | 25, 35, 50, 65, 120           | 120             | 12          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28(1)<br>/PLCC 32 |

| - 4KX9 FAST     | MK45H04  | 25, 35, 50, 65, 120           | 120             | 12          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28 (1)            |

| - 8KX9 FAST     | MK45H08  | 25, 35, 50, 65, 120           | 120             | 12          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 28                |

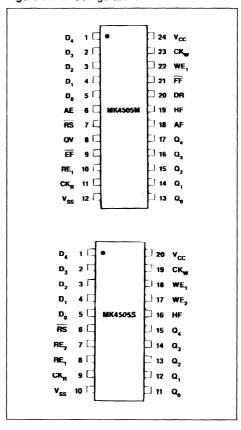

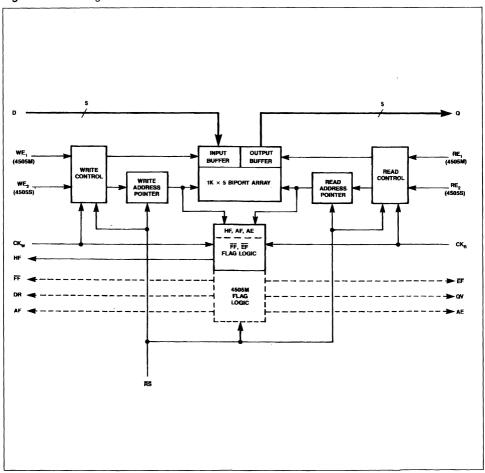

| - 1KX9 dk 40MHz | MK4505 M | 25, 33, 50                    | 100             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 24                |

| MASTER & SLAVE  | MK4505 S | 25, 33, 50                    | 100             | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 20                |

| - 64X5X2        | MK45264  | 55, 70                        | 60              | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 24                |

| BIDIRECTIONAL   | MK45265  | 55, 70                        | 60              | NA          | NA           | 5V + 10 - 10% | 0 to + 70°C | P DIP 24                |

<sup>(1) 600</sup> mil and 300 mil PDIP.

# STATIC RAM

|                            |           |                      | 3             | 000  |       |         |             |                      |                        |

|----------------------------|-----------|----------------------|---------------|------|-------|---------|-------------|----------------------|------------------------|

| ORGANISATION               | PART      | SPEEDIS              | 3             | F    | CMOS  | CCDR    | S           | TEMP RANGE           | PACKAGE                |

| DESRIPTION                 | NUMBER    |                      | ACTIVE @ ns   | STBY | STBY  | HA<br>H |             |                      |                        |

| – 4KX1                     | IMS1203   | 25, 35, 45           | 88            | 15   | 13    |         | 5V + 10-10% | 0 °C to 70 °C        | P DIP 18               |

| – 1KX4                     | IMS1223   | 25, 35, 45           | 100           | 15   | æ     |         | 5V + 10-10% | 0 °C to 70 °C        | P DIP 18               |

| – 2KX8                     | MK6116    | 150, 200, 250        | 20            | က    | -     | -       | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 24<br>/SOIC 28   |

| – 2KX8<br>LOW POWER        | MK6116L   | 150, 200, 250        | 02            | က    | 0.001 | -       | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 24<br>/SOIC 28   |

| – 2KX8                     | MKI6116   | 150, 200, 250        | 55            | က    | -     | -       | 5V + 10-10% | -40° Cto+105°C       | P DIP 24<br>/SOIC 28   |

| – 2KX8<br>LOW POWER        | MKI6116L  | 150, 200, 250        | 55            | က    | 0.01  | -       | 5V + 10-10% | -40 ° C to + 105 ° C |                        |

| - 16KX1 FAST CS            | MK41H66   | 20, 25, 35           | 120           | 10   |       |         | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 20               |

| - 16KX1                    | IMS1403   | 25, 35, 45, 55       | 75            | 15   | 9     |         | 5V + 10-10% | 0 °C to 70 °C        | P DIP/LCC 20           |

| – 16KX1                    | MK41H67   | 20, 25, 35           | 120           | 10   | 0.05  | 20      | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 20               |

| – 4KX4                     | MK41H68   | 20, 25, 35           | 120           | 8    | 0.05  | 20      | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 20               |

| – 4KX4                     | IMS1423   | 25, 35, 45, 55       | 105@25 100@35 | 15   | 0.01  |         | 5V + 10-10% | 0 °C to 70 °C        | P DIP/LCC 20<br>SOJ 20 |

| - 4KX4 FAST CS             | MK41H69   | 20, 25, 35           | 120           | 80   |       |         | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 20               |

| – 4KX4 OE                  | MK41H78   | 20, 25, 35           | 120           | 9    | 0.05  | 20      | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 22               |

| -4KX4 OE+FLASH CLR MK41H79 | MK41H79   | 20, 25, 35           | 120           | 16   | 0.05  | 20      | 5V + 10-10% | 0 °C to + 70 °C      | P DIP 22               |

| – 64KX1                    | IMS1600   | 25, 35, 45, 55       | 77@25 70@35   | 52   | 15    |         | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/LCC 22<br>SOJ 24 |

| – 64KX1                    | IMS1601   | 35, 45, 55           | 70            | 15   | 5     | 100     | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/LCC 22<br>SOJ 24 |

| -64KX1                     | IMS1605   | 15, 20, 25           | 100           | 52   | 10    | 350     | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/LCC 22<br>SOJ 24 |

| – 16KX4                    | IMS1620   | 25, 35, 45, 55       | 110@25 100@35 | 52   | 17    | A       | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/LCC 22<br>SOJ 24 |

| – 16KX4                    | IMS1625   | 15, 20, 25           | 100           | 55   | 10    | 320     | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/LCC 22<br>SOJ 24 |

| – 16KX4 OE                 | IMS1624   | 25, 35, 45, 55       | 110@25 100@35 | 52   | 17    |         | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/SOJ 24<br>LCC 28 |

| – 16KX4 OE                 | IMS1629   | 15, 20, 25           | 100           | 52   | 10    | 350     | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/SOJ 24<br>LCC 28 |

| – 16KX4 OE Sep I/O         | IMS1626/7 | 15, 20, 25           | 100           | 25   | 10    | 350     | 5V + 10-10% | 0 °C to + 70 °C      | P DIP/SOJ 28<br>LCC 28 |

| – 8KX8 OE                  | IMS1630L  | 45, 55, 70, 100, 120 | 06            | 8    | 10    | 320     | 5V + 10-10% | 0 °C to + 70 °C      | P DIP /SOIC 28         |

# STATIC RAM (Continued)

| MOTE A GILLA COCC         | F 0 4 C     |                | 3             | ICC ma     |      | Ç      |             |                  |                        |

|---------------------------|-------------|----------------|---------------|------------|------|--------|-------------|------------------|------------------------|

| DESCRIPTION               | NUMBER      | SPEEDns        | ACTIVE @ ns   | ∏.<br>STBY | CMOS | ₽<br>₹ | VCC         | TEMP RANGE       | PACKAGE                |

| – 8KX8 OE                 | MK48H64     | 70, 120        | 100@70 90@120 | 2          | 200  | 200    | 5V + 10-10% | 0 °C to + 70 °C  | P DIP 28<br>/SOIC 28   |

| – 8KX8 OE                 | MK48H64L    | 70, 120        | 100@70 90@120 | 5          | 0.05 | 25     | 5V + 10-10% | 0 °C to + 70 °C  | P DIP 28<br>/SOIC 28   |

| - 8KX8 OE                 | IMS1635     | 15, 20, 25     | 100           | 22         | 5    | 320    | 5V + 10-10% | 0 °C to + 70 °C  | P DIP 28               |

| - 8KX9 OE                 | MK48H89     | 20, 25, 35     | 120           | 22         | -    | 200    | 5V + 10-10% | 0 °C to + 70 °C  | P DIP 28               |

| – 8KX9 OE                 | IMS1695     | 15, 20, 25     | 100           | 25         | 10   | 320    | 5V + 10-10% | 0 °C to + 70 °C  | P DIP/SOJ 28<br>LCC 32 |

| - 8KX8\9 PARITY           | MK48H98\99  | 20, 30, 40     | 120           | 52         | -    | 200    | 5V + 10-10% | 0 °C to + 70 °C  | P DIP 28               |

| –256KX1                   | IMS1800     | 25, 30, 35, 45 | 120           | 30         | 15   |        | 5V + 10-10% | 0 °C to + 70 ° C | P DIP/SOJ 24<br>LCC 28 |

| –64KX4                    | IMS1820     | 25, 30, 35, 45 | 120           | 30         | 15   |        | 5V + 10-10% | 0 °C to + 70 ° C | P DIP/SOJ 24<br>LCC 28 |

| - 32KX8 OE                | MK4832      | 70, 120        | 70            | က          | -    | 200    | 5V + 10-10% | 0 °C to + 70 ° C | P DIP 28               |

| - 32KX8 OE                | MK4832L     | 70, 120        | 70            | က          | 0.05 | 2      | 5V + 10-10% | 0 °C to + 70 °C  | P DIP 28               |

| – 128KX8                  | (1) MK48127 | 55, 70, 85     | 80            | က          | 0.2  | 150    | 5V + 10-10% | 0 °C to + 70 ° C | P DIP 32<br>/SOJ 32    |

| – 128KX8<br>CHIP ENABLE 2 | 1) MK48128  | 55, 70, 85     | 80            | 3          | 0.2  | 150    | 5V + 10-10% | 0 °C to + 70 ° C | P DIP 32<br>/SOJ 32    |

(1) Product preview.

# MILITARY PRODUCTS

| ORGANISATION<br>DESCRIPTION | PART<br>NUMBER  | Speed ns                   | Active current (mA @ ns) | ICC max<br>Stdby 1 | lcc max<br>Stdby 2 | СС <sub>ря</sub><br>(9 3% | Vœ                  | Temp Range  | Packages         |

|-----------------------------|-----------------|----------------------------|--------------------------|--------------------|--------------------|---------------------------|---------------------|-------------|------------------|

| -4KX1                       | IMS1203M        | 25, 35, 45                 | 80 mA                    | 15 mA              | 10 mA              |                           | 5±10%               | - 55 to 125 | DIP, F-PACK      |

| - 1KX4                      | IMS1223M        | 25, 35, 45                 | 110 mA                   | 15 mA              | 10 mA              |                           | 5±10%               | - 55 to 125 | DIP, F-PACK      |

| - 16KX1                     | IMS1400M        | 45, 55, 70                 | 120 mA                   | 30 mA              | (3)                |                           | 2 <del>+</del> 10 % | - 55 to 125 | DIP, LCC         |

| - 16KX1                     | IMS1403M        | 35, 45, 55                 | 75 mA                    | 15 mA              | 10 mA              |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| – 16KX1                     | IMS1403LM       | 35, 45, 55                 | 75 mA                    | 15 mA              | 10 mA              | 400 JuA                   | 5±10%               | - 55 to 125 | DIP, LCC         |

| - 16KX1                     | MKB41H67        | 25, 35, 45                 | 115 mA                   | 10 mA              | 0,05 mA            |                           | 5±10%               | - 55 to 125 | DIP 20           |

| – 2KX8                      | MKB6116         | 150, 200, 250 70 mA        | 70 mA                    | 10 mA              | 0,1 mA             |                           | 5±10%               | - 55 to 125 | DIP 24           |

| -512X9 (FIFO)               | MKB4501         | 100, 120, 140,<br>175, 235 | 90 mA                    | 8 mA               | 0,9 mA             |                           | 5 ± 10 %            | - 55 to 125 | DIP 24           |

| – 4KX4                      | IMS1420M        | 55, 70                     | 120 mA                   | 30 mA              | (3)                |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| - 4KX4                      | IMS1423M        | 35, 45, 55                 | 130@35, 110@55 20 mA     | 20 mA              | 15 mA              |                           | 5±10%               | - 55 to 125 | DIP, LCC, F-PACK |

| - 64KX1                     | IMS1600M        | 45, 55, 70                 | 70 mA                    | 25 mA              | 19 mA              |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| -64KX1                      | IMS1601M        | 45, 55, 70                 | 70 mA                    | 20 mA              | 15 mA              | 1200 µA                   | 5±10%               | - 55 to 125 | DIP, LCC         |

| - 16KX4                     | IMS1620M        | 45, 55, 70                 | 100 mA                   | 30 mA              | 20 mA              |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| – 16KX4                     | IMS1620LM       | 45, 55, 70                 | 100 mA                   | 20 mA              | 8 mA               | 1200 µA                   | 5 ± 10 %            | - 55 to 125 | DIP, LCC         |

| – 16KX4                     | IMS1624M (1)    | 45, 55, 70                 | 100 mA                   | 30 mA              | 20 mA              |                           | 5 ± 10 %            | - 55 to 125 | DIP, LCC         |

| – 16KX4                     | IMS1624LM (1)   | 45, 55, 70                 | 100 mA                   | 20 mA              | 8 mA               | 1200 JuA                  | 5 ± 10 %            | - 55 to 125 | DIP, LCC         |

| – 8KX8                      | IMS1630M        | 45, 55, 70                 | 85 mA                    | 30 mA              | 20 mA              |                           | 5 ± 10 %            | - 55 to 125 | DIP, LCC         |

| – 8KX8                      | IMS1630LM       | 45, 55, 70                 | 85 mA                    | 30 mA              | 20 mA              | 1200 µA                   | 5±10%               | - 55 to 125 | DIP, LCC         |

| -64KX1                      | IMS1605M        | 20, 25, 35                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| – 16KX4                     | IMS1625M        | 20, 25, 35                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| – 16KX4                     | IMS1629M (1)    | 20, 25, 35                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| – 16KX4                     | IMS1626M (1, 2) | 20, 25, 35                 |                          |                    |                    |                           | 2 ± 10 %            | - 55 to 125 | DIP, LCC         |

| - 16KX4                     | IMS1627M (1, 2) | 20, 25, 35                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| - 8KX8                      | IMS1635M (1)    | 20, 25, 35                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| 8KX9                        | IMS1695M (1)    | 20, 25, 35                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| - 256KX1                    | IMS1800M        | 30, 35, 45                 |                          |                    |                    |                           | 5±10%               | - 55 to 125 | DIP, LCC         |

| - 64KX4                     | IMS1820M        | 30, 35, 45                 |                          |                    |                    |                           | 5 ± 10 %            | - 55 to 125 | OP I CO          |

(2) Separate I/O

Stdby 1 : Stable Input, TTL Levels

Stdby 2 : Cycling Input, CMOS Levels

| AMD       | SGS-THOMSON<br>Group |

|-----------|----------------------|

| AM2147    | IMS1203              |

| AM2148/9  | IMS1223              |

| AM2167    | IMS1403              |

| AM2168    | IMS1423 or MK41H68   |

| AM9126    | MK6116               |

| AM99C68   | IMS1423 or MK41H68   |

| AM99C88   | MK48H64              |

| AM99C89   | MK48H89              |

| AM67C4501 | MK4501/H01           |

| AM67C4502 | MK45H02              |

| AM67C4503 | MK4503/H03           |

| DALLAS<br>Semiconductor | SGS-THOMSON<br>Group |

|-------------------------|----------------------|

| DS2009                  | MK4501/H01           |

| DS2010                  | MK45H02              |

| DS2011                  | MK4503/H03           |

| DS2012                  | MK45H04              |

| DS1210                  | MK48Z02              |

| DS1225                  | MK48Z08              |

| DS1243                  | MK48T08              |

| DS1287                  | MK48T87              |

| DS1235                  | MK48Z30              |

| DS1230                  | MK48Z30A             |

| CYPRESS  | SGS-THOMSON<br>Group |

|----------|----------------------|

| CY2147   | IMS1203              |

| CY2148/9 | IMS1223              |

| CY7C147  | IMS1203              |

| CY7C148  | IMS1223              |

| CY7C164  | IMS1620              |

| CY7C166  | IMS1624              |

| CY7C167  | IMS1403 or MK41H67   |

| CY7C168  | MK41H68              |

| CY7C185  | IMS1630L             |

| CY7C187  | IMS1600              |

| CY7194   | IMS1820              |

| CY7C197  | IMS1800              |

| CYC412   | MK4501/H01           |

| CY7C424  | MK45H02              |

| CYC429   | MK4503/H03           |

| FUJITSU | SGS-THOMSON<br>Group |

|---------|----------------------|

| MB81C67 | IMS1403 orMK41H67    |

| MB81C68 | IMS1423 or MK41H68   |

| MB81C71 | IMS1600              |

| MB81C74 | IMS1620              |

| MB81C75 | IMS1624              |

| MB81C78 | MK48H64              |

| HARRIS   | SGS-THOMSON<br>Group |

|----------|----------------------|

| HM65747  | IMS1203              |

| HM65748  | IMS1223              |

| HM65767  | IMS1403              |

| HM65261  | IMS1403              |

| HM65768  | IMS1423 or MK41H68   |

| HM65787  | IMS1600              |

| HM65764  | IMS1630L             |

| HM6116/L | MK6116/L             |

| HM20256  | MK4832               |

| HITACHI | SGS-THOMSON<br>Group |

|---------|----------------------|

| HM6116  | MK6116               |

| HM6147  | IMS1203              |

| HM6148  | IMS1223              |

| HM6167  | IMS1403              |

| HM6168  | IMS1423 or MK41H79   |

| HM6264  | MK48H64              |

| HM6267  | IMS1403              |

| MICRON<br>Technology | SGS-THOMSON<br>Group |

|----------------------|----------------------|

| MT5C1601             | IMS1403 or MK41H67   |

| MT5C1604             | IMS1423 or MK41H68   |

| MT5C6401             | IMS1600              |

| MT5C6404             | IMS1620              |

| MT5C6405             | IMS1624              |

| HYUNDAI | SGS-THOMSON<br>Group |

|---------|----------------------|

| HY6116  | MK6116               |

| HY61C68 | MK41H68              |

| HY61C67 | MK41H67              |

| HY62256 | MK4832               |

| HY62C87 | IMS1600              |

| HY62C88 | IMS1620              |

| HY6264  | MK48H64              |

| MITSUBISHI | SGS-THOMSON<br>Group |

|------------|----------------------|

| M5M21C67P  | IMS1403              |

| M5M21C68P  | IMS1423 or MK41H68   |

| M5M5165P   | IMS1630 or MK48H64   |

| M5M5187P   | IMS1600              |

| M5M5188P   | IMS1620              |

| M5M5178P   | IMS1630              |

| M5M5256    | MK4832               |

| IDT      | SGS-THOMSON<br>Group |

|----------|----------------------|

| IDT6167A | IMS1403 or MK41H67   |

| IDT6168  | IMS1423 or MK41H68   |

| IDT7164  | IMS1630              |

| IDT7187  | IMS1600              |

| IDT7188  | IMS1620              |

| IDT7198  | IMS1624              |

| IDT7201  | MK4501/H01           |

| IDT7202  | MK4502/H02           |

| IDT7103  | MK4503/H03           |

| IDT7204  | MK45H04              |

| IDT7105  | MK45H08              |

| IDT6178S | MK41H80 or MK41S80   |

| IDT7174  | MK48H74              |

| MOTOROLA | SGS-THOMSON<br>Group |

|----------|----------------------|

| MCM1423  | IMSZ1420 or MH41H66  |

| MCM6064  | MK48H64              |

| MCM6164L | IMS1630 L            |

| MCM6168  | IMS1420L or MH41H68  |

| MCM6264  | MK48H98              |

| MCM6268  | MK41H68              |

| MCM6268  | IMS1423 or MK41H68   |

| MCM6269  | IMS1421              |

| MCM6287  | IMS1601L             |

| MCM6287  | IMS1600              |

| MCM6288  | IMS1620              |

| MCM6290  | IMS1624              |

| MCM4180  | MK41H80 or MK41S80   |

| NEC      | SGS-THOMSON<br>Group |

|----------|----------------------|

| μPD2147  | IMS1203              |

| μPD4311  | IMS1403 orMK41H67    |

| μPD21467 | IMS1403 or MK41H67   |

| μPD4314  | IMS1423 or MK41H68   |

| μPD4361  | IMS1600              |

| μPD4362  | MK48H64IMS1630       |

| μPD4364  | MK48H64              |

| μPD43256 | MK4832               |

| SONY    | SGS-THOMSON<br>Group |

|---------|----------------------|

| CXK5816 | MK6116               |

| CXK5416 | MK41H68              |

| CXK5864 | MK48H64              |

| CXK5854 | MK48H64              |

| ОКІ     | SGS-THOMSON<br>Group |

|---------|----------------------|

| MSM5165 | MK48H64              |

| MSM5188 | MK4832               |

| TOSHIBA | SGS-THOMSON<br>Group |  |  |  |

|---------|----------------------|--|--|--|

| TC55416 | IMS1620              |  |  |  |

| TC55417 | IMS1624              |  |  |  |

| TC5561  | IMS1600              |  |  |  |

| TMM2068 | IMS1423              |  |  |  |

| TMM315  | IMS1203              |  |  |  |

| TMM5562 | IMS1620              |  |  |  |

| SARRATOGA | SGS-THOMSON<br>Group |  |  |  |

|-----------|----------------------|--|--|--|

| SSM2148   | IMS1223              |  |  |  |

| SSM2149   | IMS1223              |  |  |  |

| SSM6167   | IMS1403 orMK41H67    |  |  |  |

| SSM6168   | IMS1423 orMK41H68    |  |  |  |

| SSM7164   | IMS1630L             |  |  |  |

| SSM7166   | IMS1624              |  |  |  |

| SSM7188   | IMS1620              |  |  |  |

| SSL4180   | MK41H80              |  |  |  |

| SSM6170   | MK41H78              |  |  |  |

| SSL7201   | MK4501/H01           |  |  |  |

| SSL7203   | MK4503/H03           |  |  |  |

| UMC    | SGS-THOMSON<br>Group |

|--------|----------------------|

| UM4501 | MK4501               |

| UM4502 | MK4502               |

| UM6116 | MK6116               |

| VITELIC | SGS-THOMSON<br>Group |  |  |  |

|---------|----------------------|--|--|--|

| V61C67  | IMS1403 or MK41H67   |  |  |  |

| V61C68  | IMS1423 or MK41H68   |  |  |  |

| V62C16  | MK6116               |  |  |  |

| V62C64  | MK48H64              |  |  |  |

| V62C256 | MK4832               |  |  |  |

| VLSI    | SGS-THOMSON<br>Group |  |  |  |

|---------|----------------------|--|--|--|

| VT20C50 | IMS1423 or MK41H68   |  |  |  |

| VT20C68 | IMS1423 or MK41H68   |  |  |  |

| VT20C69 | IMS1423 or MK41H68   |  |  |  |

| VT62K54 | IMS1620              |  |  |  |

### STANDARD MILITARY DRAWING REFERENCE

| SMD Number INMOS Part Number |              |  |  |  |  |

|------------------------------|--------------|--|--|--|--|

| 4K X 1 (IMS 1203)            |              |  |  |  |  |

| 5962-8751301VC               | SMD1203S-25M |  |  |  |  |

| 5962-8751301XC               | SMD1203A-25M |  |  |  |  |

| 5962-8751302VC               | SMD1203S-35M |  |  |  |  |

| 5962-8751302XC               | SMD1203A-35M |  |  |  |  |

| 5962-8751303VC               | SMD1203S-45M |  |  |  |  |

| 5962-8751303XC               | SMD1203A-45M |  |  |  |  |

| 1K X 4 (I                    | MS1223)      |  |  |  |  |

| 5962-8751304VC               | SMD1223S-25M |  |  |  |  |

| 5962-8751304XC               | SMD1223A-25M |  |  |  |  |

| 5962-8751305VC               | SMD1223S-35M |  |  |  |  |

| 5962-8751305XC               | SMD1223A-35M |  |  |  |  |

| 5962-8751306VC               | SMD1223S-45M |  |  |  |  |

| 5962-8751306XC               | SMD1223A-45M |  |  |  |  |

| 16K X 1 (                    | IMS1403)     |  |  |  |  |

| 8413202RC                    | SMD1403S-45M |  |  |  |  |

| 8413202YA                    | SMD1403N-45M |  |  |  |  |

| 8413205RC                    | SMD1403S-35M |  |  |  |  |

| 8413205YA                    | SMD1403N-35M |  |  |  |  |

| 8413208RC                    | SMD1403S-55M |  |  |  |  |

| 8413208YA                    | SMD1403N-55M |  |  |  |  |

| 4K X 4 (I                    | MS1423)      |  |  |  |  |

| 5962-8670512RC               | SMD1423S-35M |  |  |  |  |

| 5962-8670512XA               | SMD1423N-35M |  |  |  |  |

| 5962-8670512ZC               | SMD1423Y-35M |  |  |  |  |

| 5962-8670513RC               | SMD1423S-45M |  |  |  |  |

| 5962-8670513XA               | SMD1423N-45M |  |  |  |  |

| 5962-8670513ZC               | SMD1423Y-45M |  |  |  |  |

| 5962-8670514RC               | SMD1423S-55M |  |  |  |  |

| 5962-8670514XA               | SMD1423N-55M |  |  |  |  |

| 5962-8670514ZC               | SMD1423Y-55M |  |  |  |  |

| 5962-8670515RC               | SMD1423S-70M |  |  |  |  |

| 5962-8670515XA               | SMD1423N-70M |  |  |  |  |

| 5962-8670515ZC               | SMD1423Y-70M |  |  |  |  |

| SMD Number     | INMOS<br>Part Number |  |  |  |

|----------------|----------------------|--|--|--|

| 64K X 1 (IMS1  | 600:IMS1601L)        |  |  |  |

| 5962-8601503XC | SMD1600S-45M         |  |  |  |

| 5962-8601503ZA | SMD1600N-45M         |  |  |  |

| 5962-8601504XC | SMD1601S-45LM        |  |  |  |

| 5962-8601504ZA | SMD1601N-45LM        |  |  |  |

| 5962-8601505XC | SMD1600S-55M         |  |  |  |

| 5962-8601505ZA | SMD1600N-55M         |  |  |  |

| 5962-8601506XC | SMD1601S-55LM        |  |  |  |

| 5962-8601506ZA | SMD1601N-55LM        |  |  |  |

| 5962-8601507XC | SMD1600S-70M         |  |  |  |

| 5962-8601507ZA | SMD1600N-70M         |  |  |  |

| 5962-8601508XC | SMD1601S-70LM        |  |  |  |

| 5962-8601508ZA | SMD1601N-70LM        |  |  |  |

| 16K X 4 (      | IMS1624)             |  |  |  |

| 5962-8685911LC | SMD1624S-70LM        |  |  |  |

| 5962-8685911XA | SMD1624N-70LM        |  |  |  |

| 5962-8685912LC | SMD1624S-70M         |  |  |  |

| 5962-8685912XA | SMD1624N-70M         |  |  |  |

| 5962-8685913LC | SMD1624S-55LM        |  |  |  |

| 5962-8685913XA | SMD1624N-55LM        |  |  |  |

| 5962-8685914LC | SMD1624S-55M         |  |  |  |

| 5962-8685914XA | SMD1624N-55M         |  |  |  |

| 5962-8685915LC | SMD1624S-45LM        |  |  |  |

| 5962-8685915XA | SMD1624N-45LM        |  |  |  |

| 5962-8685916LC | SMD1624S-45M         |  |  |  |

| 5962-8685916XA | SMD1624N-45M         |  |  |  |

| 8K X 8 (I      | MS1630)              |  |  |  |

| 5962-8552504XC | SMD1630S-70M         |  |  |  |

| 5962-8552504YA | SMD1630N-70M         |  |  |  |

| 5962-8552505XC | SMD1630S-55M         |  |  |  |

| 5962-8552505YA | SMD1630N-55M         |  |  |  |

| 5962-8552510XC | SMD1630S-55LM        |  |  |  |

| 5962-8552510YA | SMD1630N-55LM        |  |  |  |

| 5962-8552511XC | SMD1630S-70LM        |  |  |  |

| 5962-8552511YA | SMD1630N-70LM        |  |  |  |

# **COMMERCIAL SRAMs**

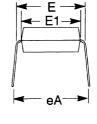

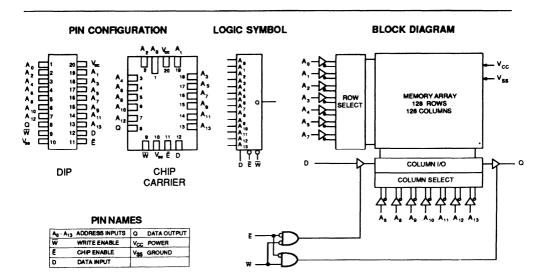

# IMS1203 **CMOS** High Performance 4K x 1 Static RAM

### **FEATURES**

- · INMOS' Very High Speed CMOS

- · Advanced Process 1.6 Micron Design Rules

- · 4K x 1 Bit Organization

- 25, 35, and 45 nsec Access Times

- · 25, 35, and 45 nsec Chip Enable Access Times

- · Fully TTL Compatible

- · Separate Data Input and Output

- · Three-state Output

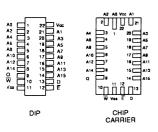

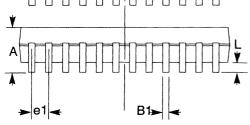

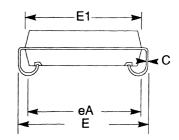

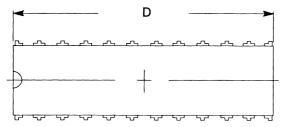

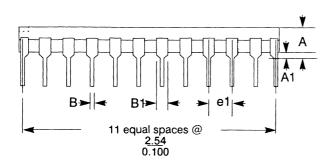

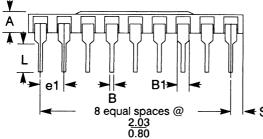

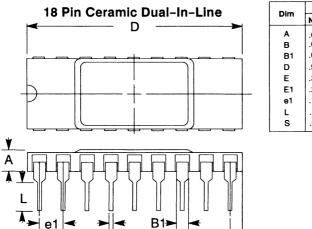

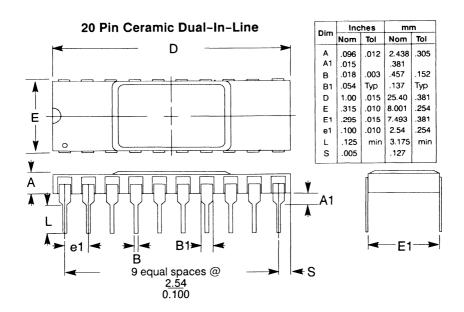

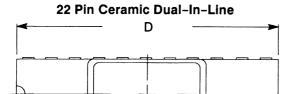

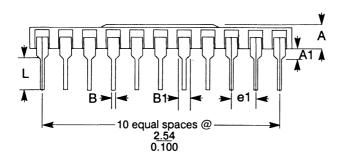

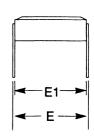

- 18 Pin, 300-mil DIP

- Single +5V ± 10% Operation

- Power Down Function

### DESCRIPTION

The INMOS IMS1203 is a high performance 4Kx1 CMOS static RAM. The IMS1203 allows speed enhancements to existing 4Kx1 applications with the additional benefit of reduced power consumption.

The IMS1203 features fully static operation requiring no external clocks or timing strobes, and equal address access and cycle times. Additionally, the IMS1203 provides a Chip Enable (/E) function that can be used to place the device into a low-power standby mode.

The IMS1203M is a MIL-STD-883 version intended for military applications.

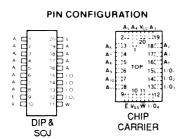

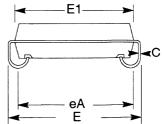

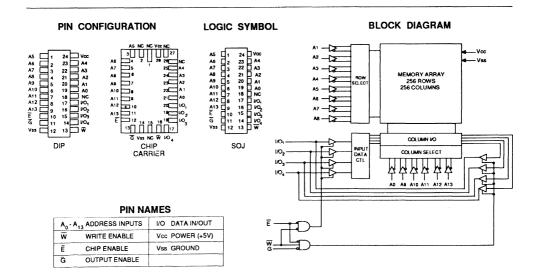

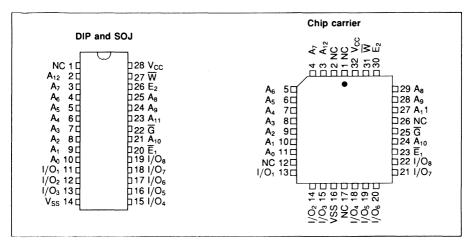

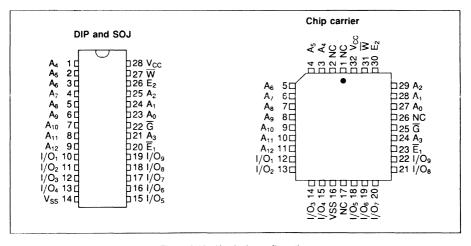

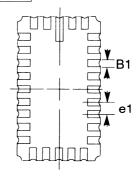

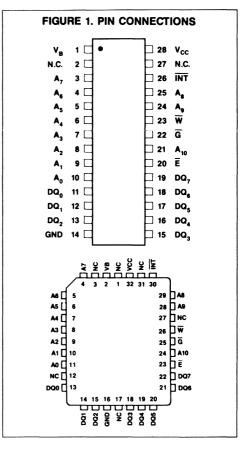

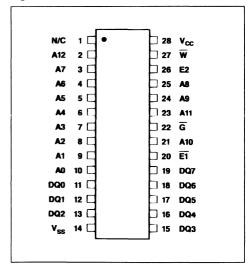

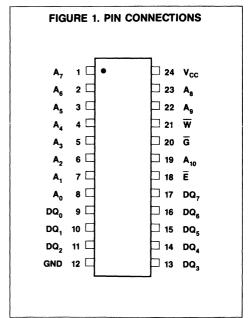

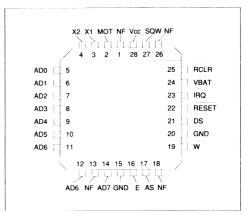

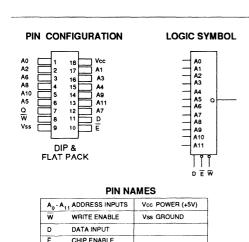

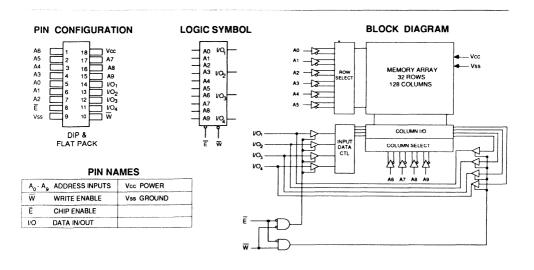

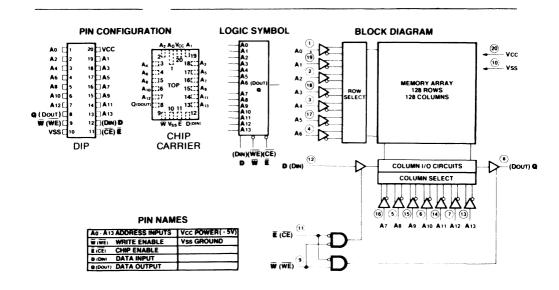

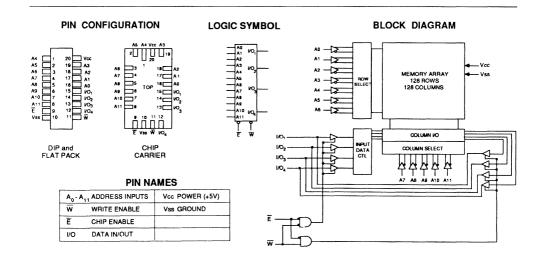

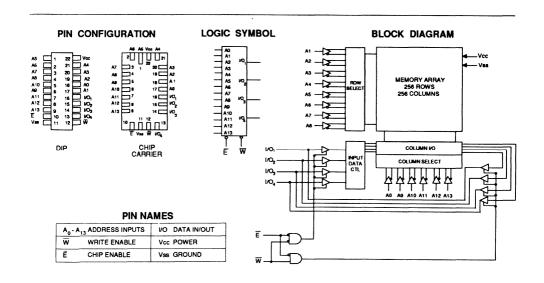

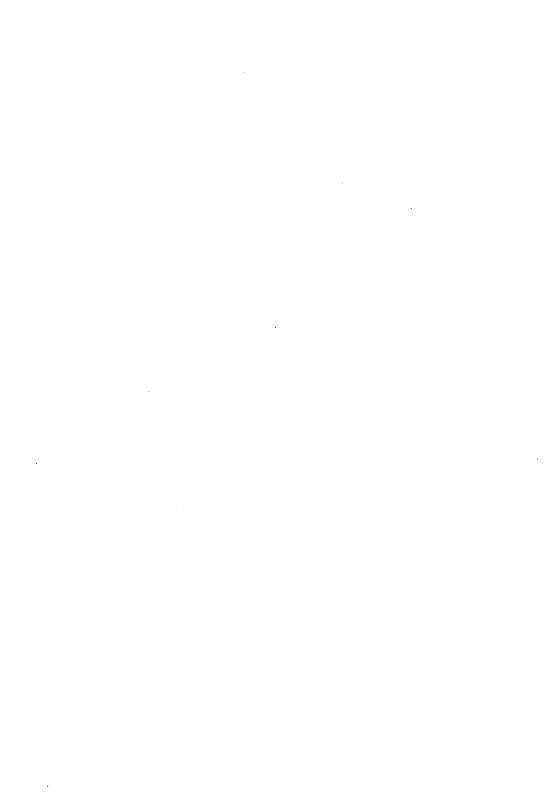

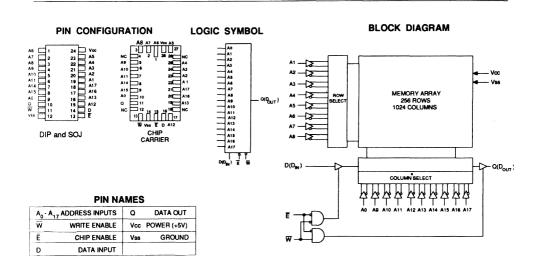

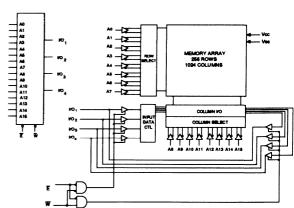

### PIN CONFIGURATION Vcc A2 A6 17 A1

Α8

A5

A10

АЗ 16

A4

A11 A7 Đ

| A ADDRESS INPUTS | Vcc POWER                             |  |  |  |

|------------------|---------------------------------------|--|--|--|

| WRITE ENABLE     | Vss GROUND                            |  |  |  |

| DATA INPUT       |                                       |  |  |  |

| CHIP ENABLE      |                                       |  |  |  |

| DATA OUTPUT      |                                       |  |  |  |

|                  | WRITE ENABLE  DATA INPUT  CHIP ENABLE |  |  |  |

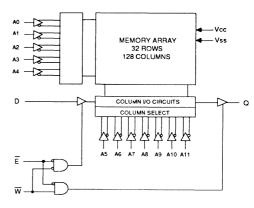

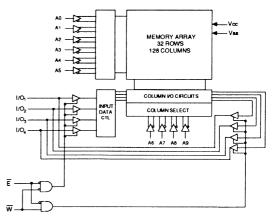

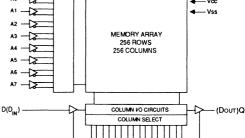

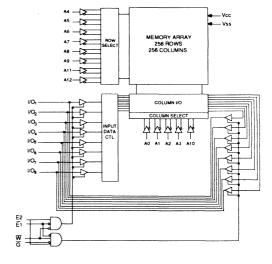

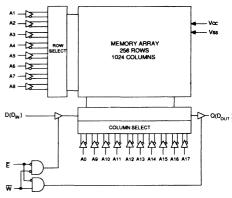

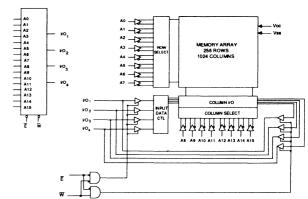

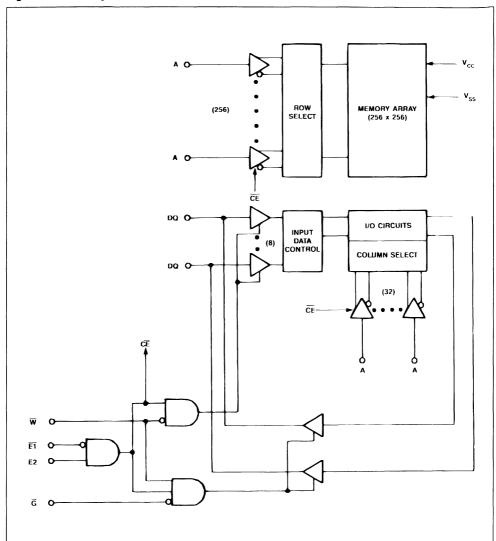

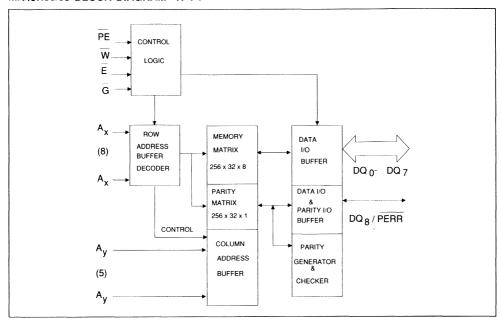

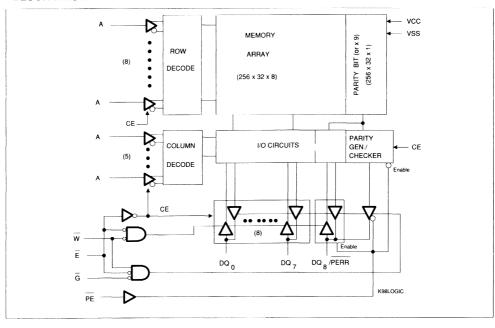

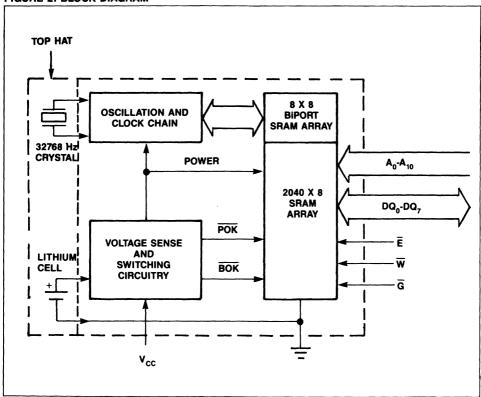

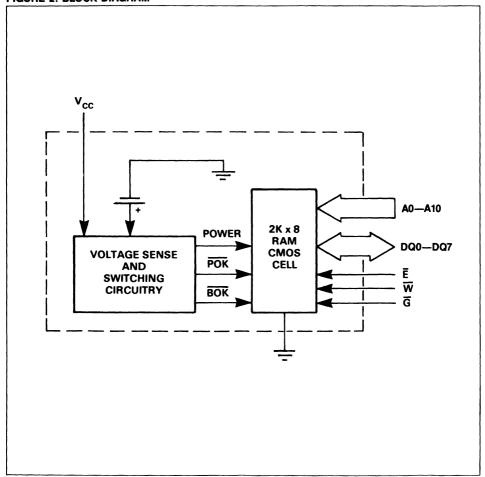

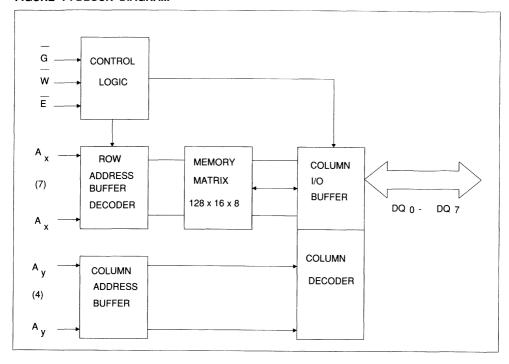

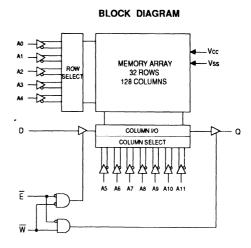

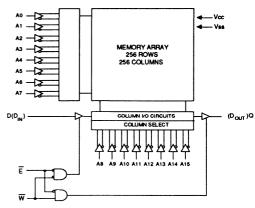

### **BLOCK DIAGRAM**

November 1989

### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to $V_{SS}$ 2.0 to 7.0V |

|-----------------------------------------------------|

| Voltage on Q $\dots$ $-1.0$ to $(V_{CC} + 0.5V)$    |

| Temperature Under Bias –55°C to 125°C               |

| Storage Temperature65°C to 150°C                    |

| Power Dissipation                                   |

| DC Output Current                                   |

| (One Second Duration)                               |

\*Stresses greater than those listed under. Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### DC OPERATING CONDITIONS

| SYMBOL          | PARAMETER                     | MIN   | TYP | MAX     | UNITS | NOTES                      |

|-----------------|-------------------------------|-------|-----|---------|-------|----------------------------|

| V <sub>CC</sub> | Supply Voltage                | 4.5   | 5.0 | 5.5     | V     |                            |

| $V_{SS}$        | Supply Voltage                | 0     | 0   | 0       | ٧     |                            |

| VIH             | Input Logic "1" Voltage       | 2.0   |     | Vcc +.5 | ٧     | All inputs                 |

| $V_{iL}$        | Input Logic "0" Voltage       | -1.0* |     | 0.8     | ٧     | All inputs                 |

| T <sub>A</sub>  | Ambient Operating Temperature | 0     |     | 70      | °C    | 400 linear ft/min air flow |

$<sup>^{\</sup>star}$  V<sub>IL</sub> Min = -3.0V for pulse width <20ns, note b.

### DC ELECTRICAL CHARACTERISTICS (0°C $\leq$ $T_A$ $\leq$ $70^{\circ}$ C) (V $_{CC}$ = 5.0V $\pm$ 10%) $^a$

| SYMBOL           | PARAMETER                                                                    | MIN | мах | UNITS | NOTES                                                                                                                                                    |

|------------------|------------------------------------------------------------------------------|-----|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>CC1</sub> | Average $V_{CC}$ Power Supply Current                                        |     | 80  | mA    | $t_{AVAV} = t_{AVAV} (min)$                                                                                                                              |

| I <sub>CC2</sub> | V <sub>CC</sub> Power Supply Current (Standby,<br>Stable TTL Input Levels)   |     | 15  | mA    | $\begin{split} \overline{E} & \geq V_{lH} \\ & \text{All other inputs } V_{lN} \\ & \leq V_{lL} \text{ or } \geq V_{lH} \end{split}$                     |

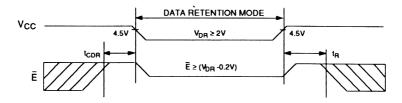

| I <sub>CC3</sub> | V <sub>CC</sub> Power Supply Current (Standby<br>Stable CMOS Input Levels)   |     | 6   | mA    | $\begin{split} \overline{E} &\geq (V_{CC} - 0.2V) \\ &\text{All other inputs at } V_{iN} \\ &\leq 0.2V \text{ or } \geq \\ &(V_{CC} - 0.2V) \end{split}$ |

| I <sub>CC4</sub> | V <sub>CC</sub> Power Supply Current (Standby.<br>Cycling CMOS Input Levels) |     | 13  | mA    | $\overline{E} \geq (V_{CC} - 0.2V)$ Inputs cycling at $V_{IN}$ $\leq 0.2V \text{ or } \geq$ $(V_{CC} - 0.2V)$                                            |

| I <sub>ILK</sub> | Input Leakage Current (Any Input)                                            |     | ±1  | μА    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                          |

| I <sub>OLK</sub> | Off State Output Leakage Current                                             |     | ±5  | μА    | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                          |

| $V_{OH}$         | Output Logic "1" Voltage                                                     | 2.4 |     | ٧     | $I_{OUT} = -4mA$                                                                                                                                         |

| V <sub>OL</sub>  | Output Logic "0" Voltage                                                     |     | 0.4 | ٧     | I <sub>OUT</sub> = 12mA                                                                                                                                  |

Note a I<sub>CC</sub> is dependent on output loading and cycle rate, the specified values are obtained with the output unloaded

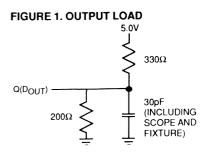

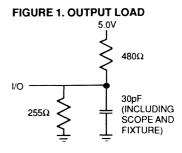

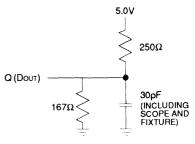

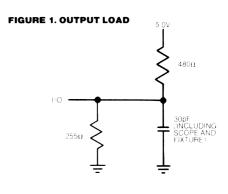

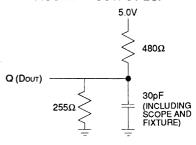

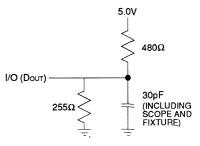

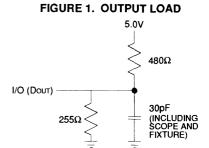

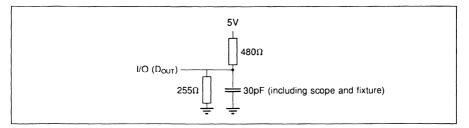

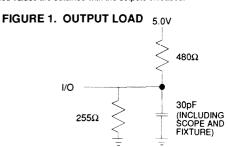

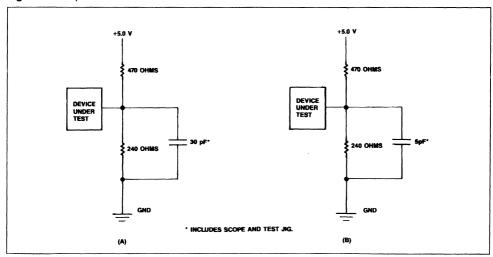

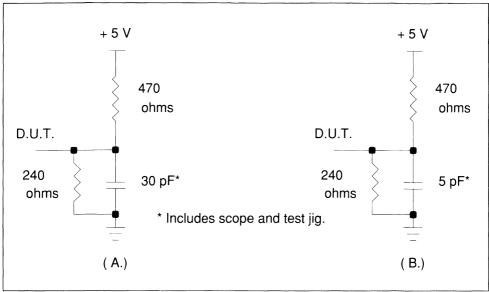

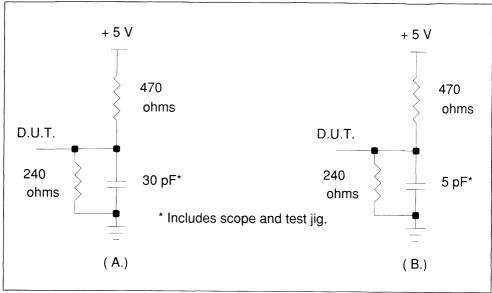

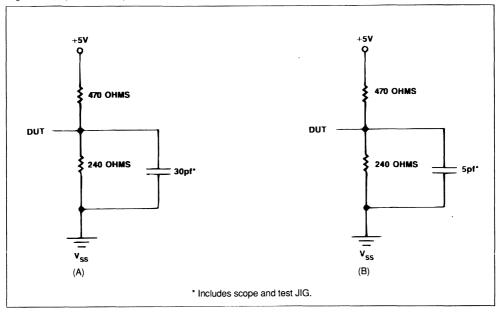

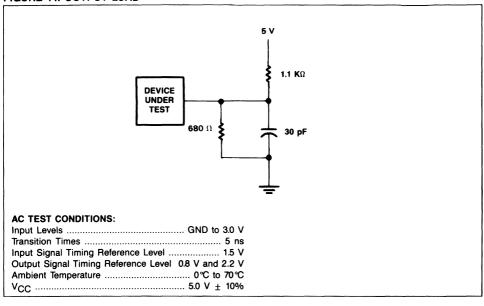

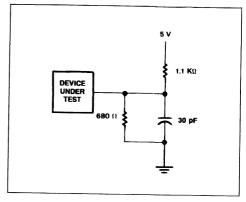

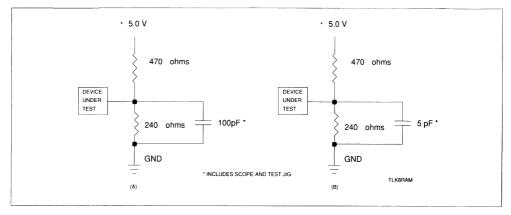

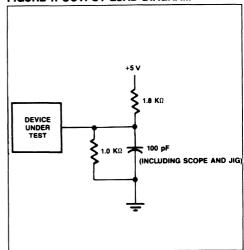

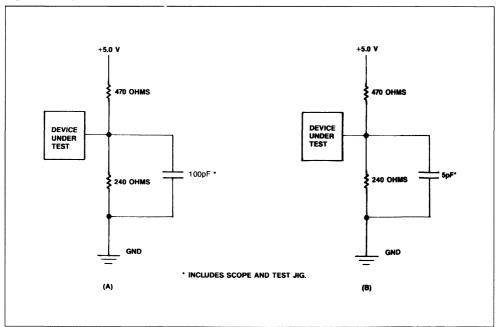

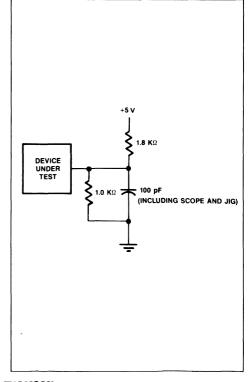

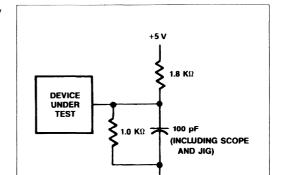

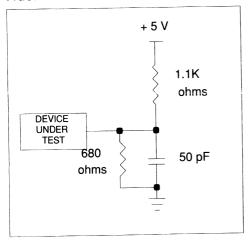

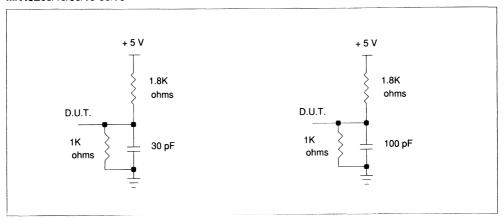

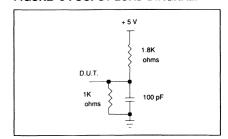

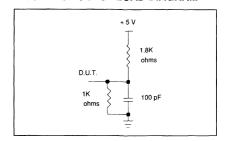

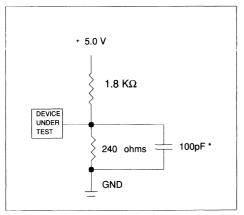

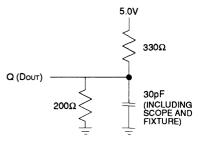

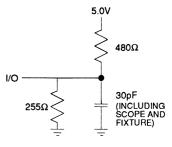

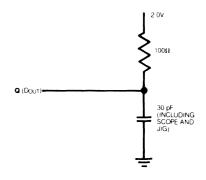

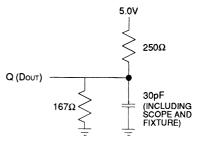

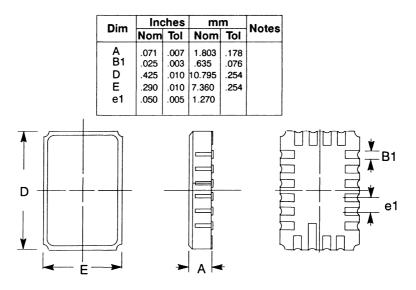

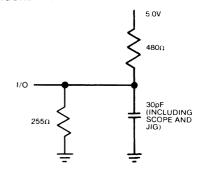

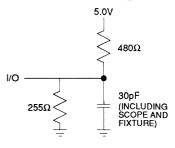

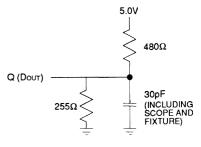

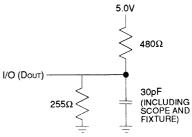

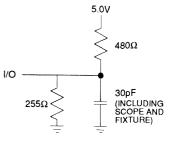

### **AC TEST CONDITIONS**

| V <sub>SS</sub> to 3V |

|-----------------------|

| 5ns                   |

| 1.5V                  |

| See Figure 1          |

|                       |

### CAPACITANCE $(T_A = 25^{\circ}C, f = 1.0 \text{ MHz})^{\circ}$

| SYMBOL          | PARAMETER          | MAX | UNITS | CONDITIONS                       |

|-----------------|--------------------|-----|-------|----------------------------------|

| C <sub>IN</sub> | Input Capacitance  | 4   | ρF    | $\Delta V = 0$ to 3V             |

| Cour            | Output Capacitance | 4   | pF    | $\triangle V = 0 \text{ to } 3V$ |

Note b. This parameter is sampled and not 100% tested

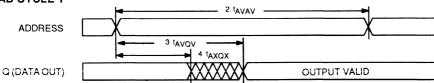

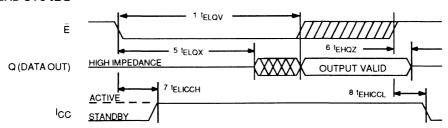

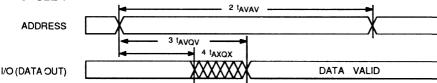

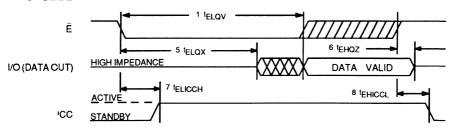

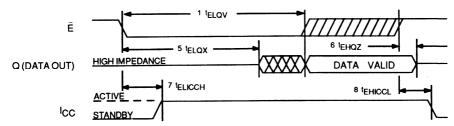

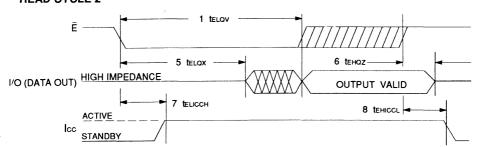

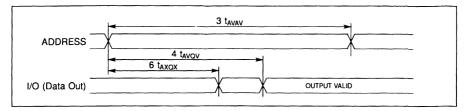

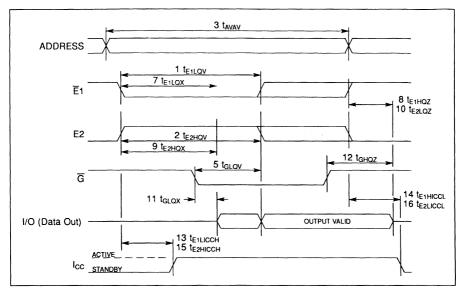

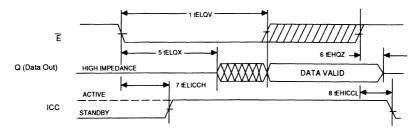

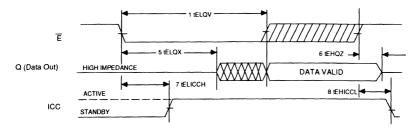

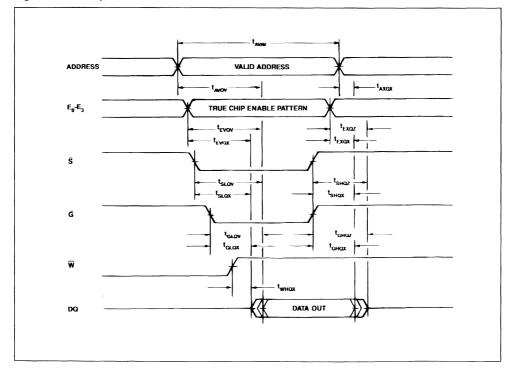

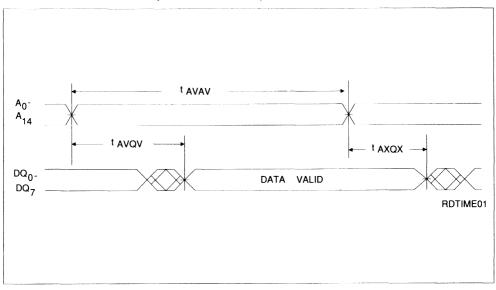

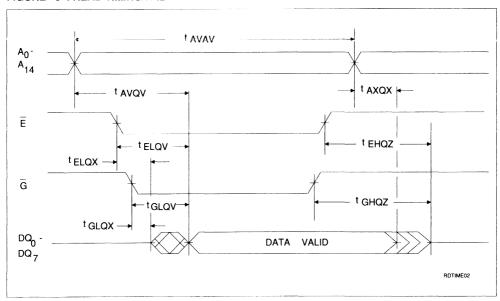

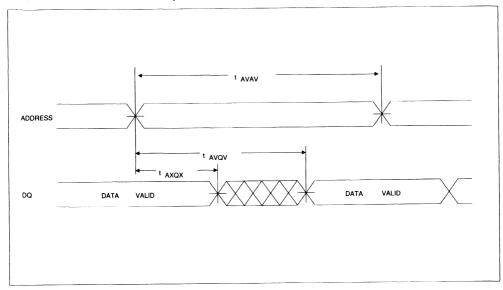

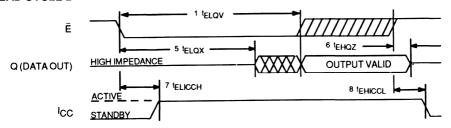

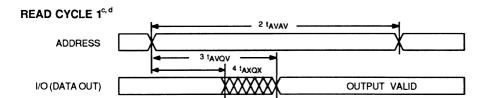

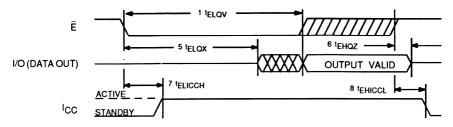

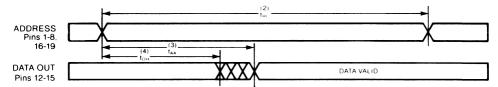

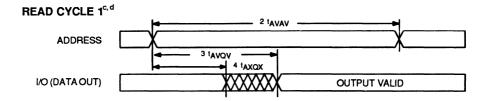

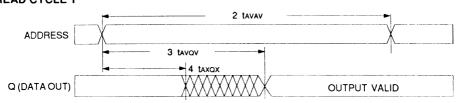

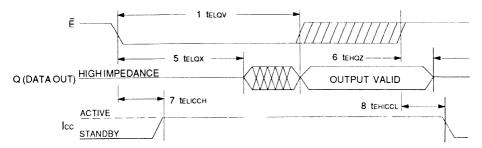

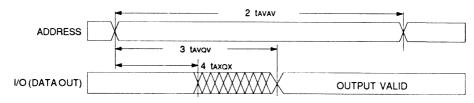

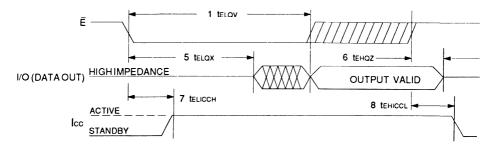

### RECOMMENDED AC OPERATING CONDITIONS (0°C $\leq$ T<sub>A</sub> $\leq$ 70°C) ( $V_{CC} = 5.0V \pm 10\%$ ) READ CYCLE9

| NO.  | SYM                 | BOL              | PARAMETER                        |     | 3-25 |     | 3-35 | 1203-45 |     | UNITS  | NOTES |

|------|---------------------|------------------|----------------------------------|-----|------|-----|------|---------|-----|--------|-------|

| 140. | Standard            | Alternate        | ININIETEN                        | MIN | MAX  | MIN | MAX  | MIN     | MAX | 011110 |       |

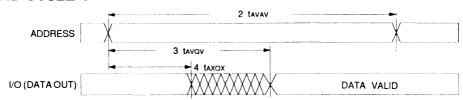

| 1    | t <sub>ELQV</sub>   | t <sub>ACS</sub> | Chip Enable Access Time          |     | 25   |     | 35   |         | 45  | ns     |       |

| 2    | t <sub>AVAV</sub>   | t <sub>RC</sub>  | Read Cycle Time                  | 25  |      | 35  |      | 45      |     | ns     | С     |

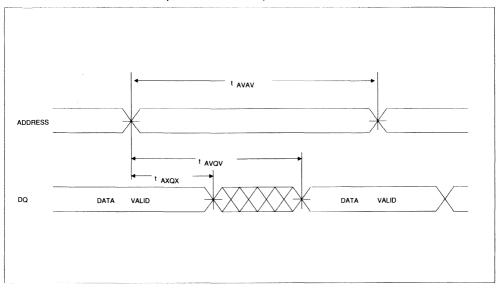

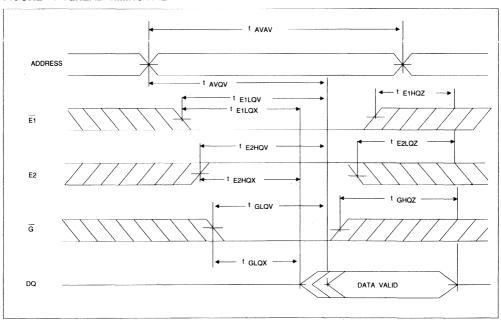

| 3    | t <sub>AVQV</sub>   | t <sub>AA</sub>  | Address Access Time              |     | 25   |     | 35   |         | 45  | ns     | d     |

| 4    | t <sub>axqx</sub>   | t <sub>OH</sub>  | Output Hold After Address Change | 3   |      | 3   |      | 3       |     | ns     |       |

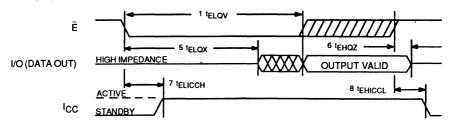

| 5    | t <sub>ELQX</sub>   | $t_{LZ}$         | Chip Enable to Output Active     | 5   |      | 5   |      | 5       |     | ns     | j     |

| 6    | t <sub>EHQZ</sub>   | $t_{HZ}$         | Chip Disable to Output Inactive  | 0   | 20   | 0   | 30   | 0       | 30  | ns     | f. j  |

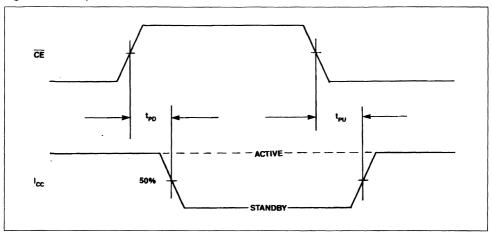

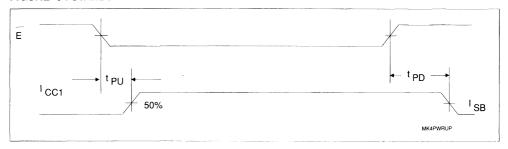

| 7    | t <sub>ELICOH</sub> | t <sub>PU</sub>  | Chip Enable to Power Up          | 0   |      | 0   |      | 0       |     | ns     | j     |

| 8    | t <sub>EHICCL</sub> | t <sub>PD</sub>  | Chip Enable to Power Down        |     | 20   |     | 20   |         | 20  | ns     | j     |

|      |                     | t <sub>T</sub>   | Input Rise and Fall Times        |     | 50   |     | 50   |         | 50  | ns     | e, j  |

Note c: For READ CYCLE 1 & 2, W is high for entire cycle.

Note d: Device is continuously selected; E low.

Note e: Measured between VIL max and VIH min.

Note f: Measured ±200mV from steady state output voltage. Load capacitance is 5pF. Note g: E and W must transition between VIH to VII or VII to VIH in a monotonic fashion.

Note j: Parameter guaranteed but not tested.

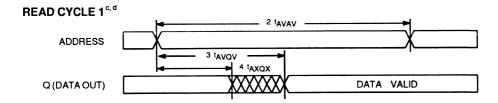

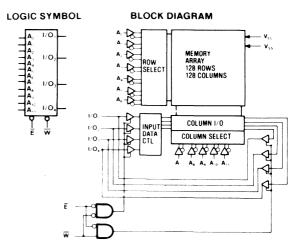

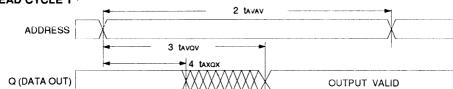

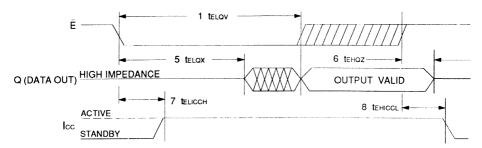

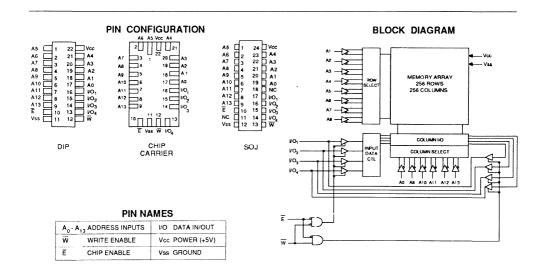

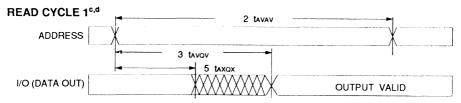

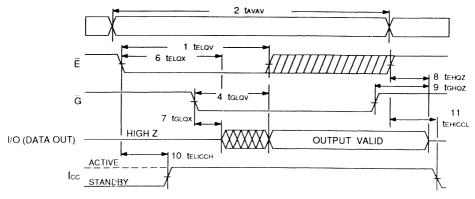

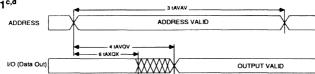

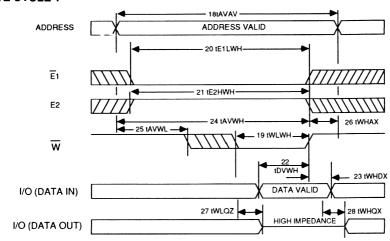

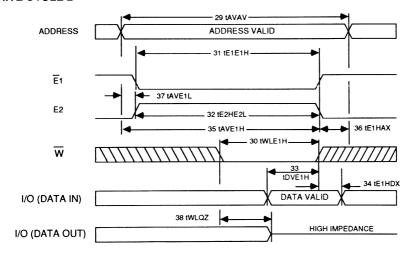

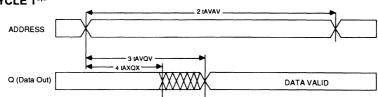

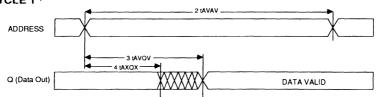

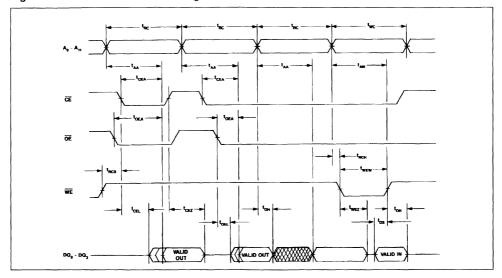

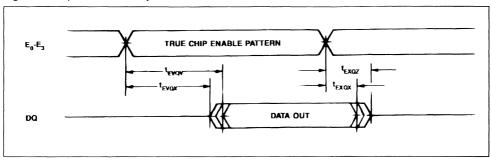

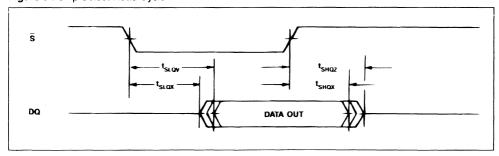

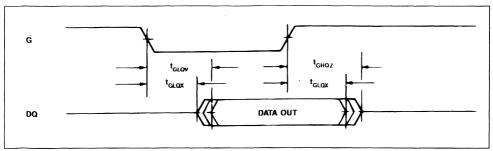

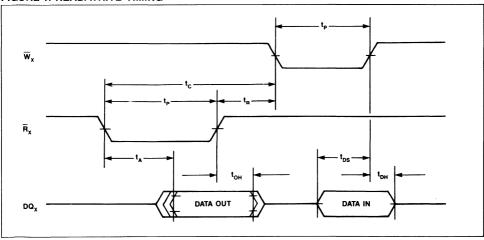

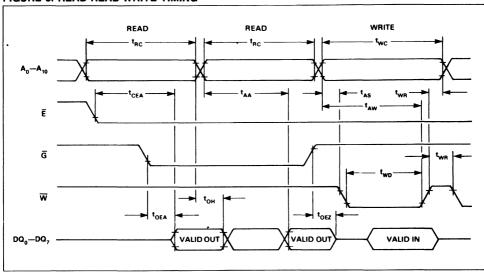

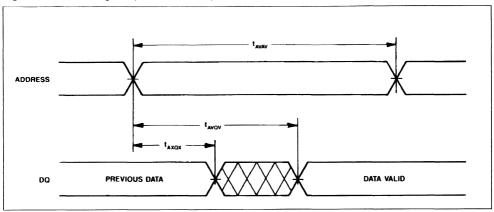

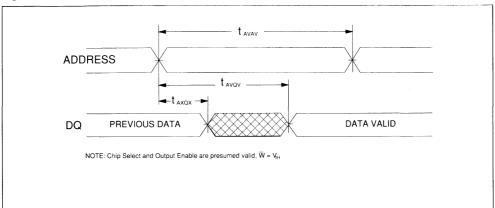

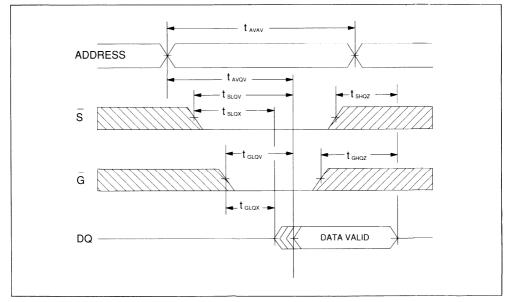

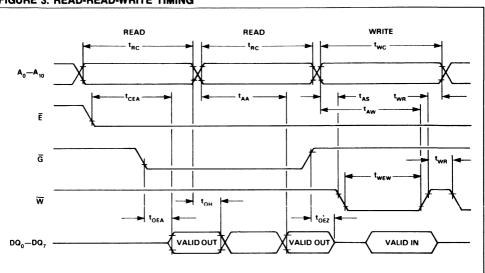

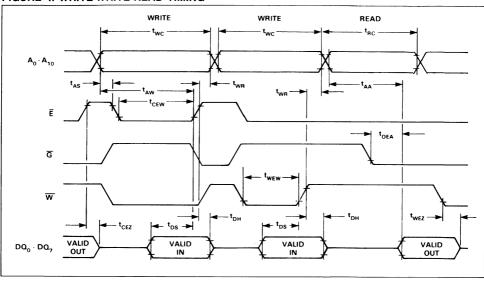

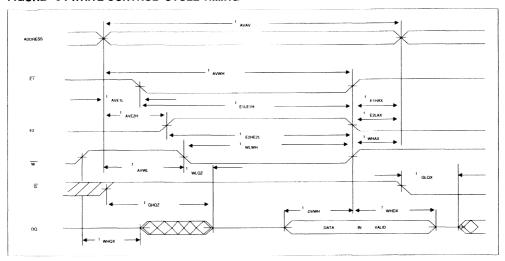

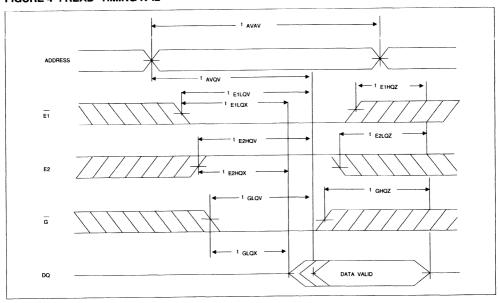

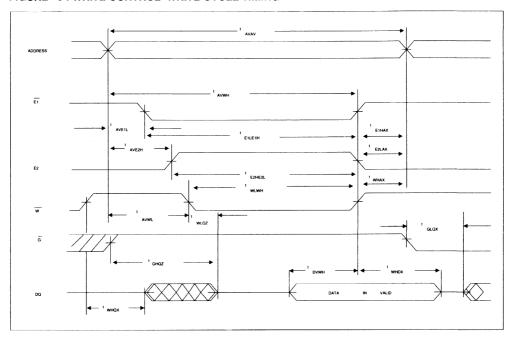

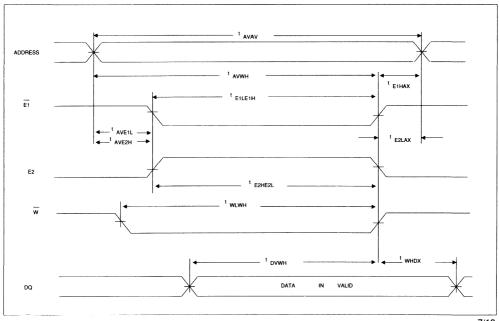

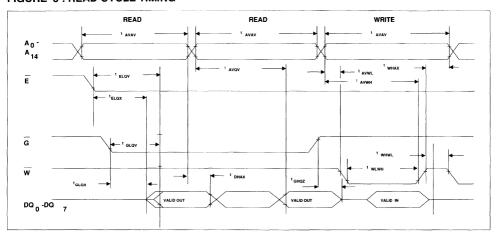

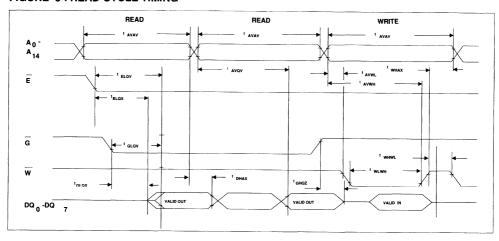

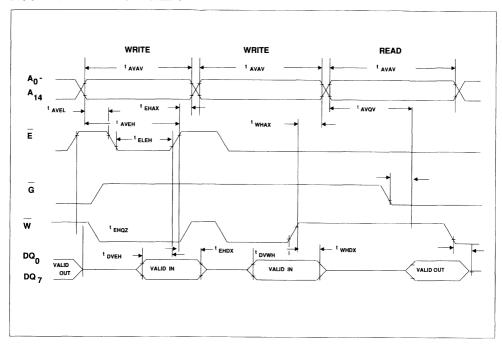

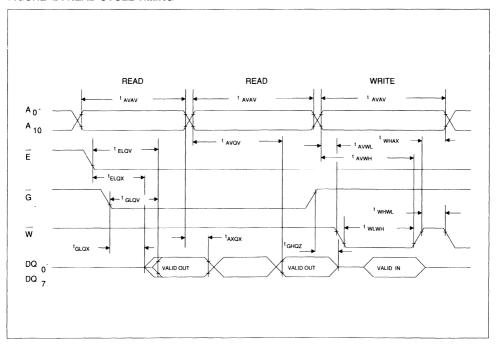

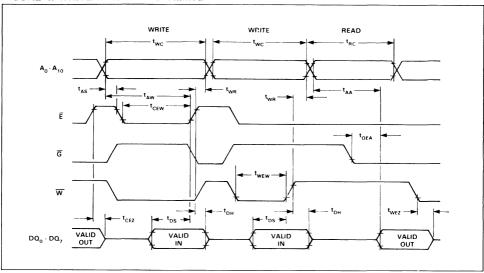

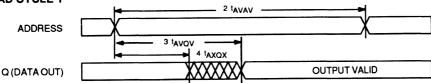

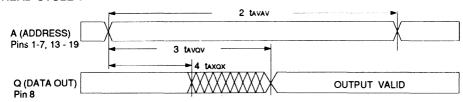

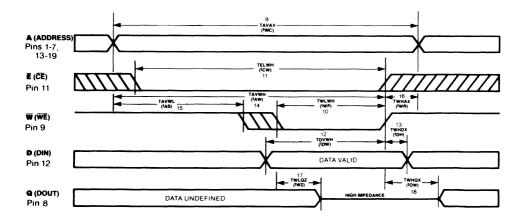

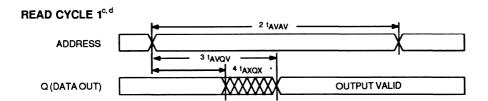

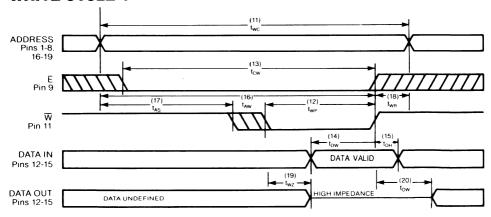

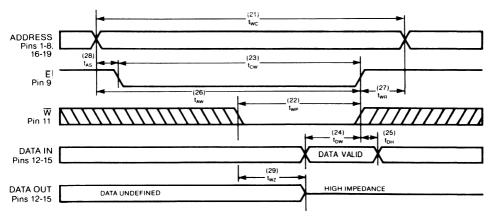

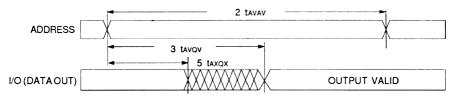

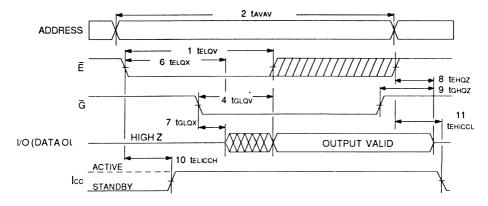

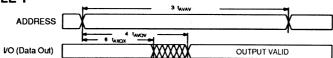

### READ CYCLE 1c, d

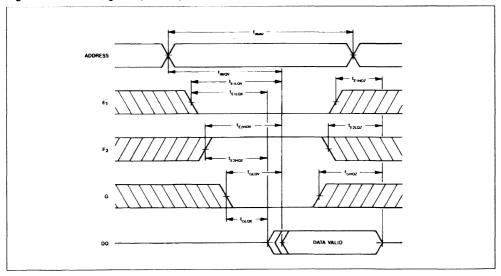

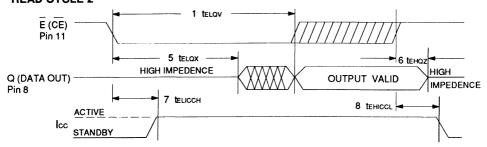

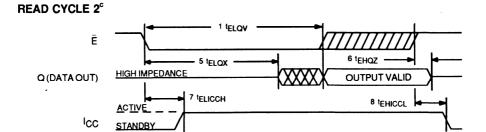

### READ CYCLE 2°

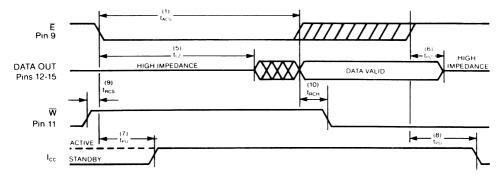

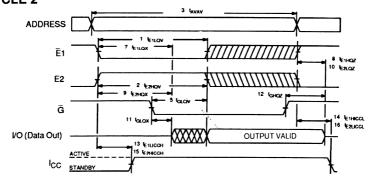

### **DEVICE OPERATION**

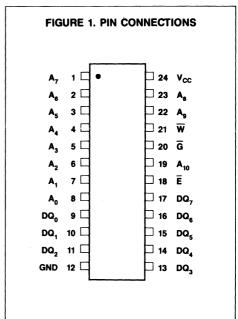

The IMS1203 has two control inputs. Chip Enable (E) and Write Enable ( $\overline{W}$ ), twelve address inputs ( $A_0$ - $A_{11}$ ). a data in  $(D_{IN})$  and a data out  $(D_{OUT})$ . The  $\overline{E}$  input controls device selection as well as active and standby modes With E low, the device is selected and the twelve address inputs are decoded to select one memory cell out of 4096. Read and Write operations on the memory cell are controlled by  $\overline{W}$  input. With  $\overline{E}$  high, the device is deselected. the output is disabled, and the power consumption is reduced to less than one-third of the active mode power with TTL levels and even lower with CMOS levels.

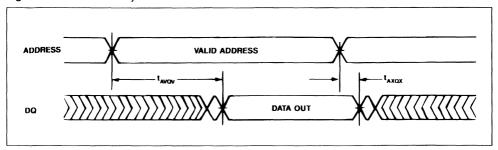

### READ CYCLE

A read cycle is defined as  $\overline{W} \supseteq V_{H}$  min with  $\overline{E} \subseteq V_{H}$  max. Read access time is measured from either E going low or from valid address.

The READ CYCLE 1 waveform shows a read access that is initiated by a change in the address inputs while E is low. The output remains active throughout READ. CYCLE 1 and is valid at the specified address access time. The address inputs may change at access time and as long as E remains low, the cycle time is equal to the address access time.

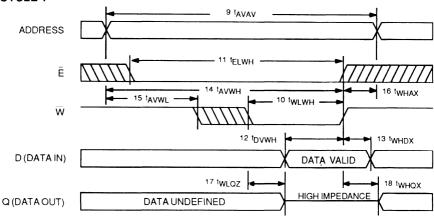

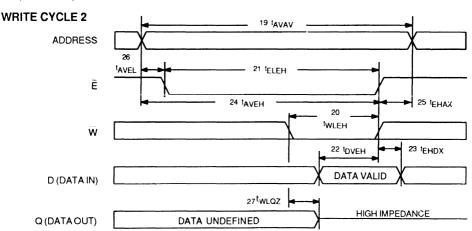

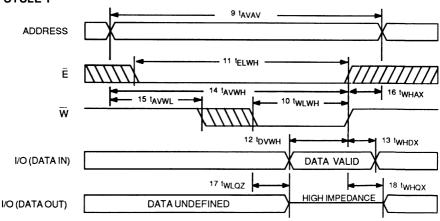

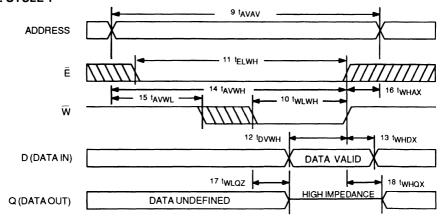

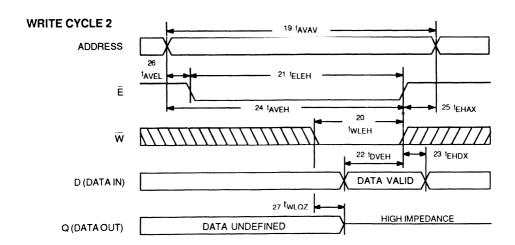

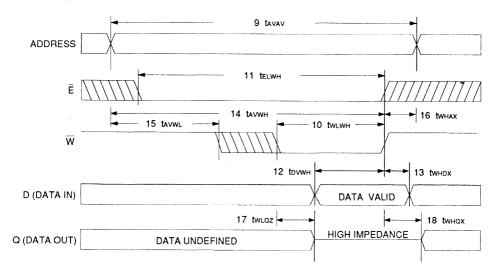

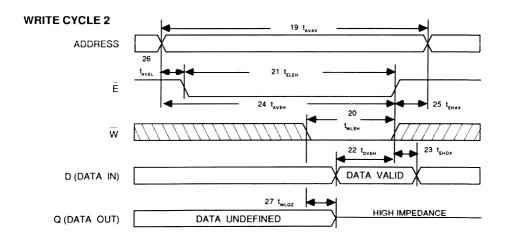

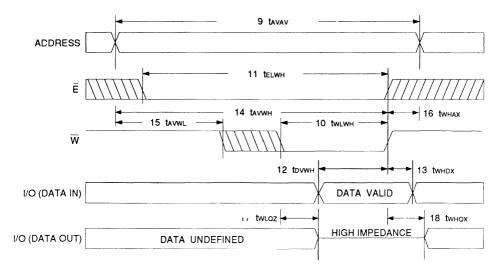

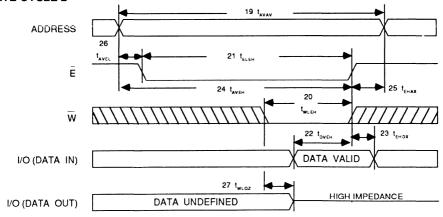

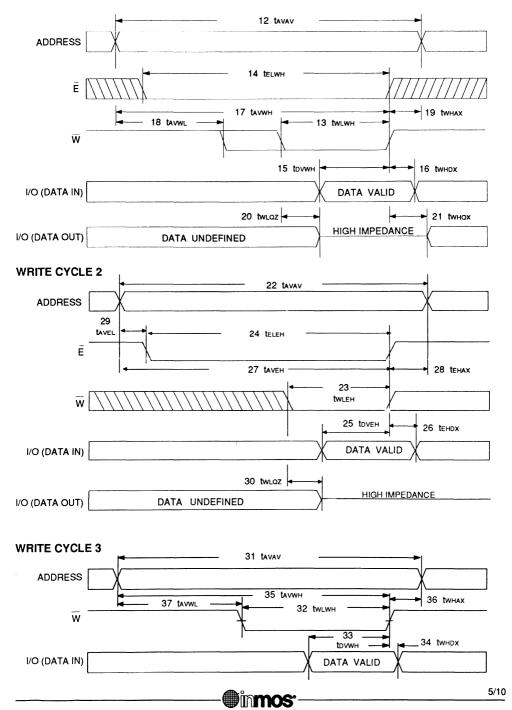

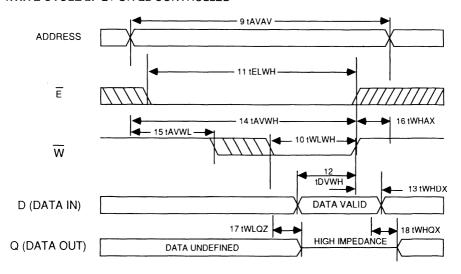

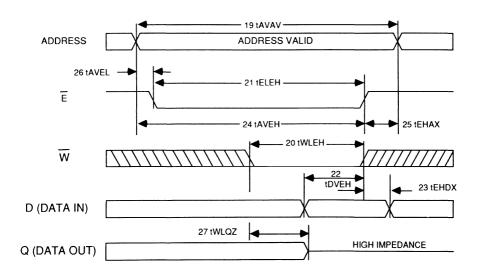

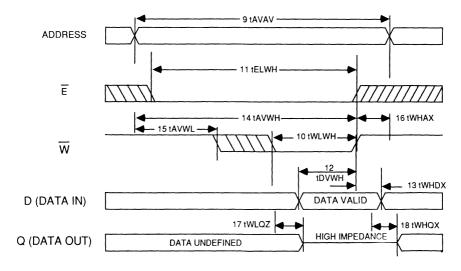

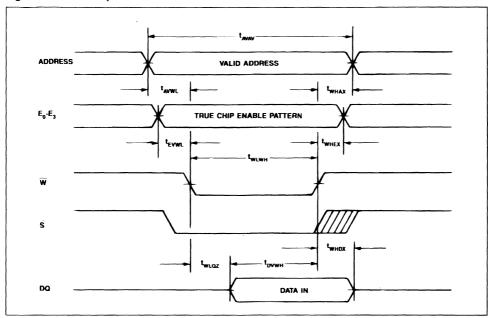

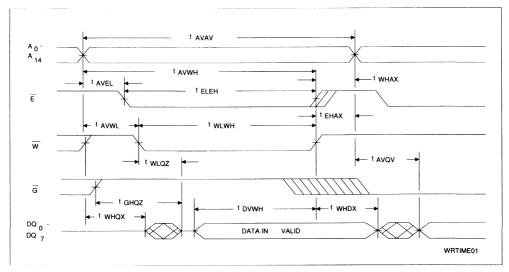

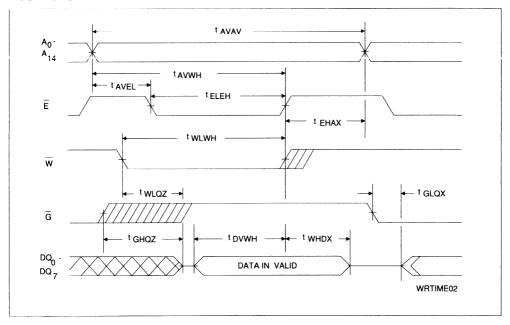

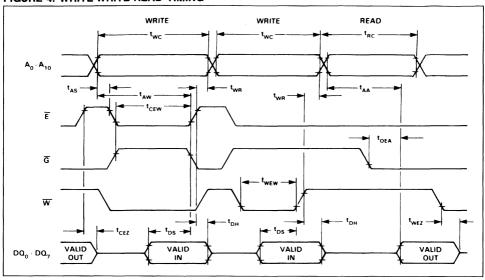

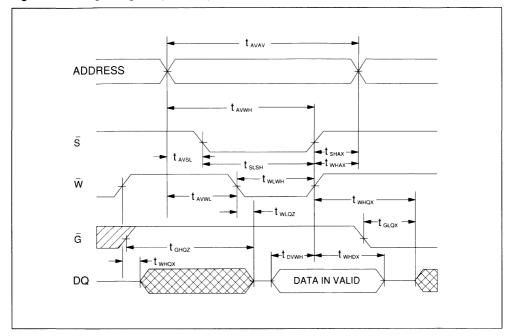

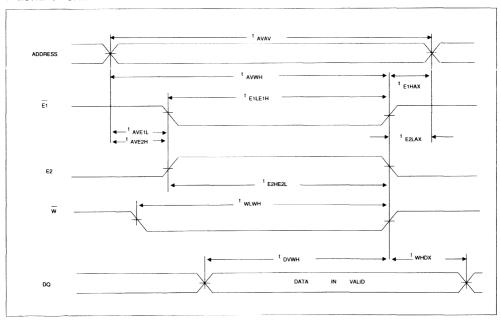

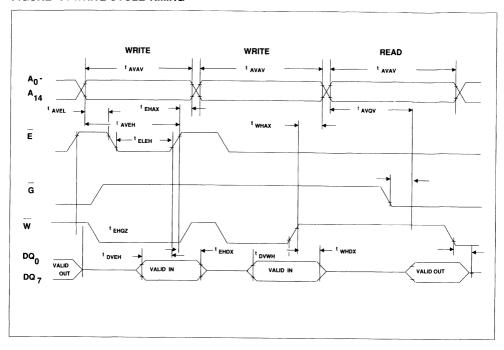

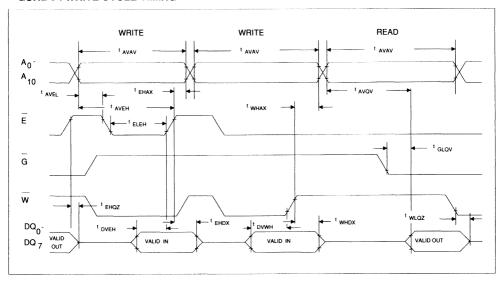

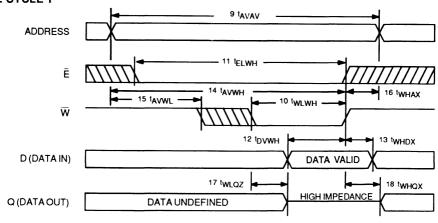

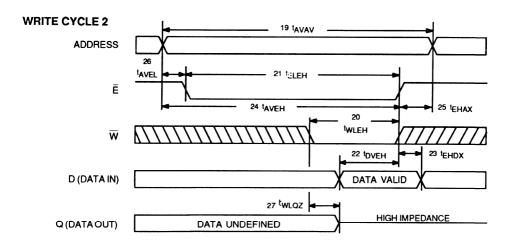

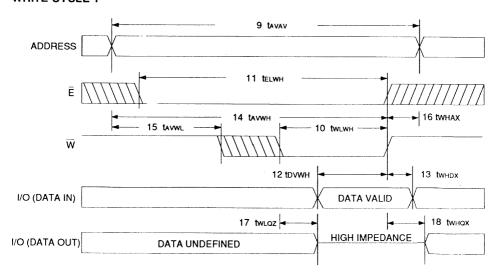

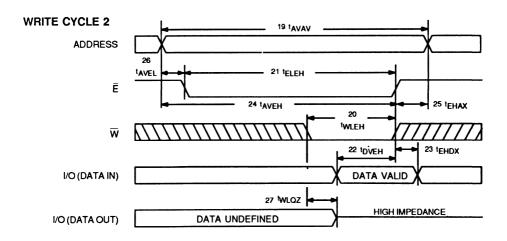

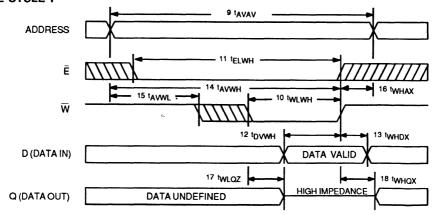

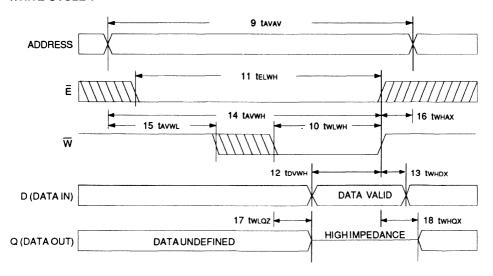

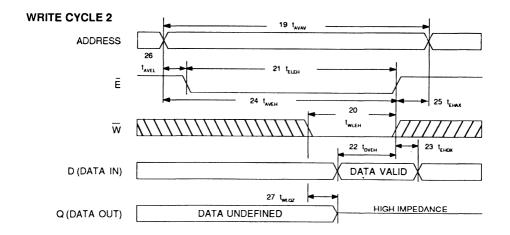

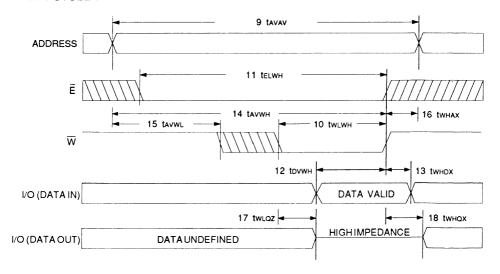

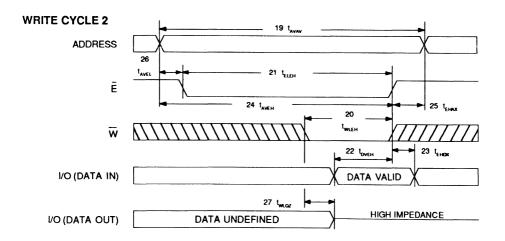

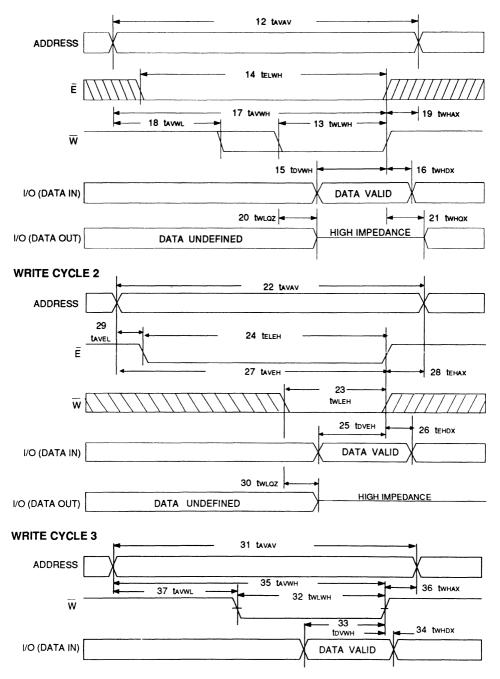

## RECOMMENDED AC OPERATING CONDITIONS (0°C $\le$ T<sub>A</sub> $\le$ 70°C) (V<sub>CC</sub> = 5.0V $\pm$ 10%) WRITE CYCLE 1: $\overline{W}$ CONTROLLED<sup>9. h</sup>